# ディジタル回路自動設計に適した プログラミングモデルと言語の研究

Practical programming models and languages for digital circuit design automation

# 照屋 大地

Daichi TERUYA

(2018年度入学, 18834303)

指導教員 中條拓伯 准教授

東京農工大学 工学府 博士後期課程 電子情報工学専攻 知能・情報工学専修 2020年度博士論文 (2021年1月31日提出)

#### 東京農工大学 工学府 博士後期課程

#### 電子情報工学専攻 知能・情報工学専修 2020 年度博士論文 要旨

題目 ディジタル回路自動設計に適したプログラミングモデルと言語の研究

提出日 2021年1月31日

ASIC や FPGA で用いるディジタル回路の設計は、ハードウェア記述言語(hardware descripttion language; HDL)を用いたレジスタ転送レベル(Resister Transfer Level; RTL)による開発が必要となる.記述の性質から HDL はバグが発生しやすく、デバッグにも様々なツールが必要で熟練した技術が必要である.そこで C/C++や Java といったプログラミング言語によって記述されたプログラムやアルゴリズムと同じふるまいをする回路を合成する技術である高位合成(high-level synthesis; HLS)と呼ばれる技術が注目され既に様々な言語による HLS ツールが開発されている.しかしながらソフトウェア開発と回路設計の記述モデルには大きな隔たりがある.ソフトウェアのプログラムには並列性やデータフローに関する情報が含まれておらず,最適化のための情報を付け加えなければスループットが非常に低くなってしまうことや,複雑で巨大なステートマシンが生成されてしまい,自動的な並列化やパイプライン化が難しい問題が発生する.

そこで本研究は,FPGA を主なターゲットとして,ソフトウェア開発の分野で生産性を高めるために用いられているプログラミングモデルによってディジタル回路設計の生産性を高めることを目的とした研究を行った.本研究は大きく分けて1)フレームワークを用いた最適なアーキテクチャの自動生成ツールの研究,2)ディジタル回路設計に近いプログラミングパラダイムを用いた回路設計ツールの研究の二つのアプローチに分けられる.

PyJer の中では Java 言語ベースの HLS ツールを利用している. HLS ツールを用いてソフトウェアとして利用されてきた既存のプログラムから回路を合成しようとした場合には,性能が低下してしまうことが一般的である. 性能低下を回避するためには回路設計の知識と HLS ツールにおける技法を熟知したエンジニアによるコードの最適化が必要となる. 筆者は,ほとんどの HLS ツールにおいてプログラムの最適化が必要であることや C や Java の一部の言語機能に制約が必要な理由は,回路設計とプログラミングのパラダイムに大きな開きがあることであると考えた.この違いによって大局的な並列性の解析や複雑なループの並列化など現在のコンパイラ技術でも困難な問題を引き起こし,ユーザによるコードの最適化を行う必要が生まれる.そこで本研究では,

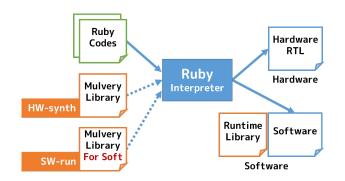

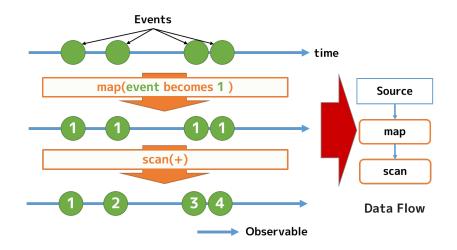

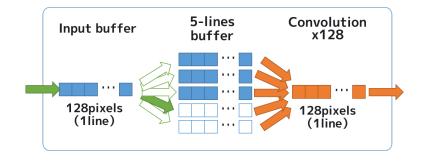

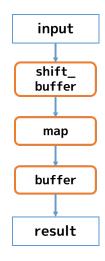

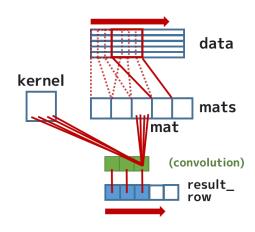

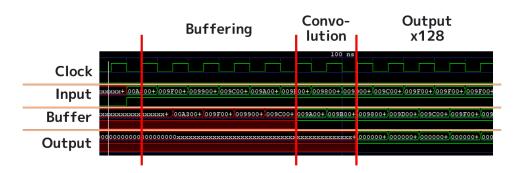

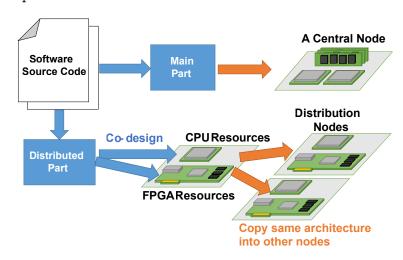

ディジタル回路設計と近いパラダイムを持ったプログラミングモデルである functional reactive programming (FRP) を用いたハードウェア設計ツール Mulvery を提案する.Mulvery は CPU と FPGA が共存するアーキテクチャにおいて利用されることを想定しフレームワーク化することで ソフトウェアとハードウェアの協調設計を実現する.画像処理を例に評価を行ったところ,5x128 ピクセルの画像と 5x5 ピクセルのフィルタの畳み込み演算を  $100 \mathrm{MHz}$  の動作周波数で 1 クロックで実行することができ,アーキテクチャ探索等を行うことなく高いスループットの回路を合成することを確認できた.また 32x32 個の LED マトリクスを用いた実験では,MCU のみでは LED マトリクスの制御さえ困難であったが,Mulvery はハードウェアオフロードによる LED マトリクス制御の高速化に加え,Ruby 言語の既存ライブラリなどを用いて Web サーバを記述することも可能で,ネットワーク経由での画像表示まで可能なものにした.

これらの応用に関する研究として,関数ポインタのサポートとクラウドコンピューティングへの FPGA の応用技術についての研究を行った.HLS においては,ポインタのように空間上の位置が動的に変化するようなプログラムを合成することは困難である.本研究で C 言語を用いる HLS ツールにおいてコードを抽象化し再利用性を高めるために重要な関数ポインタもこのような理由でサポートしコードの再利用性を高め,Mulvery のような FRP による高階関数を多用した抽象的なプログラミングモデルを実現するための研究に取り組んだ.クラウドコンピューティングの文脈では,Mulvery のデータフロー型の記述を生かし複数の FPGA で複数のタスクを分担して処理するための仕組みの基礎研究に取り組んだ.反応閾値モデルを応用した自律分散システムによって,メンテナンス性の高さと高いフォールトトレランスを実現する手法を提案した.

# 目 次

| 第1章     | 緒論                                                 | 1        |

|---------|----------------------------------------------------|----------|

| 1.1     | ハードウェアによるソフトウェアの高速化                                | 1        |

|         | 1.1.1 ハードウェアアクセラレーション                              | 1        |

|         | 1.1.2 FPGA を用いたアクセラレーション                           | 2        |

| 1.2     | ディジタル回路設計の現状と課題                                    | 3        |

|         | 1.2.1 ハードウェア記述言語を用いたディジタル回路設計                      | 3        |

|         | 1.2.2 ディジタル回路設計の生産性を高めるためのアプローチ                    | 3        |

| 1.3     | 研究目的と本稿の構成                                         | 4        |

| <b></b> |                                                    | J        |

|         | FPGA の原理と回路設計の技術                                   | 5        |

| 2.1     | FPGA の技術の概要                                        |          |

|         | 2.1.1 FPGA の原理                                     |          |

|         | 2.1.2 FPGA の EDA 技術                                |          |

|         | 2.1.3 参考文献                                         | 9        |

| 2.2     | 高位合成の原理・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・        | 9        |

|         | 2.2.1 高位合成の概要と利点                                   | 9        |

|         | 2.2.2 動作合成                                         | 9        |

|         | 2.2.3 参考文献                                         | 11       |

| 2.3     | 高速化技法                                              | 11       |

|         | 2.3.1 並行計算                                         | 11       |

| 2.4     | まとめ                                                | 12       |

| 第3章     | 関連研究                                               | 13       |

| 3.1     | はじめに・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・           |          |

| 0.1     | 3.1.1 ソフトウェア開発の技術の有効活用                             | 13       |

|         | 3.1.2 動向調査の意義                                      | 14       |

| 3.2     | カスタム回路設計ツールの種別・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ | 14       |

| 5.2     | 3.2.1 ドメイン特化言語を用いたレジスタ転送レベル設計                      | 14       |

|         | 3.2.2 汎用プログラミング言語や DSL を用いた動作レベル設計                 | 15       |

|         |                                                    | 15       |

| 3.3     | 3.2.3 ドメイン特化言語を用いたシステムレベル設計<br>既存の開発ツールの分類と特徴      |          |

| 5.5     |                                                    | 15       |

|         |                                                    | 16       |

|         | 3.3.2 HLS ツール                                      | 19       |

| 0.4     | 3.3.3 システムレベル設計ツール                                 | 21<br>23 |

| 3.4     | ᄊᄺᅲᆉᇇᄭᄼᄝᄭᆝᆝ                                        | 7.3      |

| 第4章        | フレームワークを用いたアーキテクチャレベルの最適化                                               | <b>25</b> |

|------------|-------------------------------------------------------------------------|-----------|

| 4.1        | 複数のツールを組み合わせた $\mathrm{IoT/CPS}$ エッジデバイス向けフレームワーク $\ldots$              | 25        |

|            | 4.1.1 関連研究                                                              | 26        |

|            | 4.1.2 PyJer の概要                                                         | 26        |

|            | 4.1.3 PyJer の設計方針                                                       |           |

|            | 4.1.4 PyJer が実現するシステムのアーキテクチャとデータフロー                                    | 30        |

|            | 4.1.5 PyJer <b>の使用法とその実装</b>                                            | 32        |

|            | 4.1.6 評価方法                                                              |           |

|            | 4.1.7 アプリケーションとその評価                                                     | 38        |

|            | 4.1.8 PyJer <b>の有効性の検討</b>                                              | 40        |

|            | 4.1.9 まとめ                                                               | 41        |

| 4.2        | $\mathrm{C}$ 言語ベースの $\mathrm{IoT/CPS}$ エッジデバイス向けフレームワーク $}$             | 41        |

|            | 4.2.1 はじめに                                                              | 41        |

|            | 4.2.2 新しいフレームワークのコンセプト                                                  | 41        |

|            | 4.2.3 Mulvery <b>アーキテクチャ</b>                                            |           |

|            | 4.2.4 Mulvery Core フレームワーク                                              | 44        |

|            | 4.2.5 具体的なアプリケーションの実装例                                                  | 47        |

|            | 4.2.6 データコレクタとしての活用                                                     |           |

|            | 4.2.7 まとめ                                                               | 50        |

| 第5章        | ハードウェア設計に適したプログラミング・パラダイム                                               | <b>52</b> |

| 5.1        | 背景                                                                      |           |

|            | 5.1.1 前章での研究の問題点                                                        |           |

|            | 5.1.2 関連研究および先行事例                                                       |           |

| 5.2        | Mulvery $\mathcal{I}\mathcal{V} - \mathcal{L}\mathcal{I} - \mathcal{I}$ |           |

|            | 5.2.1 Mulvery フレームワークの構成                                                |           |

|            | 5.2.2 Mulvery フレームワークを用いたシステム開発の手順                                      |           |

| 5.3        | Functional reactive programming                                         |           |

|            | 5.3.1 Reactive Programming                                              |           |

|            | 5.3.2 Observer Pattern                                                  | 58        |

|            | 5.3.3 Functional reactive programming                                   |           |

|            | 5.3.4 基本的な文法と動作                                                         |           |

| 5.4        | レジスタ転送レベル設計の合成                                                          | 60        |

|            | 5.4.1 RxRuby による記述からハードウェアを合成する手法                                       | 62        |

| 5.5        | 処理の記述の透過性                                                               | 66        |

| 5.6        | ハードウェア合成手法の性能評価と予備実験                                                    | 67        |

|            | 5.6.1 サンプルプログラム                                                         | 67        |

|            | 5.6.2 ハードウェアの合成                                                         | 67        |

|            | 5.6.3 ハードウェアの評価                                                         | 68        |

| 5.7        | ハードウェア・ソフトウェアの分割とシステムへの統合                                               | 69        |

|            | 5.7.1 ハードウェア・ソフトウェアの分割手法                                                | 69        |

| <b>.</b> . | 5.7.2 ハードウェア・ソフトウェアの連携手法                                                | 70        |

| 5.8        | アプリケーションの開発例とその評価・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                   |           |

|            | 5.8.1 フルカラー LED の制御とアプリケーションソフトウェア                                      | 71        |

|     | 5.8.2 評価                           |       |

|-----|------------------------------------|-------|

| 5.9 | 結論                                 | . 74  |

| 第6章 | HLS における関数ポインタと高階関数のサポートとその最適化     | 78    |

| 6.1 | はじめに                               | . 78  |

|     | 6.1.1 HLS と関数ポインタ                  | . 78  |

|     | 6.1.2 HLS における関数ポインタのメリット          | . 78  |

| 6.2 | 関連研究                               | . 80  |

|     | 6.2.1 定数畳み込み                       | . 80  |

|     | 6.2.2 C++のテンプレートによる関数引数            | . 80  |

|     | 6.2.3 メモリマップ型インタフェース               | . 80  |

|     | 6.2.4 Point-to 解析によってポインタ変数を取り除く方法 | . 81  |

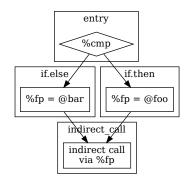

| 6.3 | 関数ポインタの削除                          | . 81  |

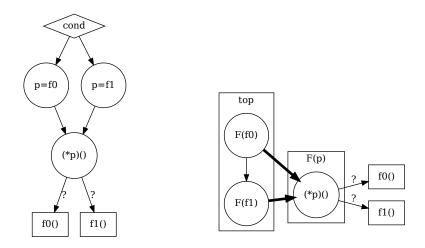

|     | 6.3.1 Callee の候補値探索                | . 83  |

|     | 6.3.2 関数ポインタを用いている命令の置換            | . 85  |

|     | 6.3.3 Void-type pointer            | . 86  |

| 6.4 | Evaluation                         | . 88  |

| 6.5 | まとめ                                | . 89  |

| 第7章 | データフロー型プログラムと分散 FPGA 環境            | 90    |

| 7.1 | はじめに                               |       |

| ••• | 7.1.1 FPGA のクラウドコンピューティングへの展開      |       |

|     | 7.1.2 FPGA 混載へテロジニアスシステム上の問題点      |       |

|     | 7.1.3 社会性昆虫の生態とその応用                |       |

|     | 7.1.4 分散システムにおける応用                 |       |

|     | 7.1.5 目的と目標                        |       |

| 7.2 |                                    |       |

|     | 7.2.1 反応閾値モデル                      |       |

|     | 7.2.2 CPU・FPGA の差別化と学習係数           |       |

| 7.3 | 新たな自律分散システムの構築                     |       |

| 7.4 |                                    |       |

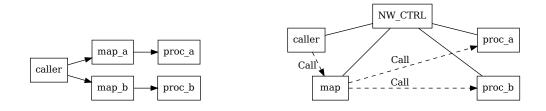

|     | 7.4.1 ハードウェア・ソフトウェアの協調設計ツール        | . 97  |

|     | 7.4.2 FPGA のクラウドサービスへの導入           |       |

| 7.5 | 統計的モデルの利用                          | . 98  |

| 7.6 |                                    | . 99  |

|     | 7.6.1 実装と実験の環境                     | . 99  |

|     | 7.6.2 実験モデル                        | . 99  |

|     | 7.6.3 実験 1: 自動スケーリングの検証            |       |

|     | 7.6.4 実験 2: 優先度の割り当て               | . 101 |

| 7.7 | クラウドシステムに向けたオートスケール機構              |       |

|     | 7.7.1 システム構成                       |       |

|     | 7.7.2 PaaS 型データ分析クラウドサービス          |       |

| 7.8 | 節のまとめ                              | 104   |

| 第8章 | 結論                          | 105 |

|-----|-----------------------------|-----|

| 8.1 | ディジタル回路設計における課題             | 105 |

| 8.2 | フレームワークによるアーキテクチャレベル最適化     | 105 |

| 8.3 | ディジタル回路の自動設計に適した言語パラダイム     | 105 |

| 8.4 | C 言語における関数ポインタと高階関数のサポート    | 106 |

| 8.5 | データフロー型プログラムの分散 FPGA 環境への応用 | 106 |

# 図目次

| 1.1               | The architecture of tipical GPU and TPU                                         | 2           |

|-------------------|---------------------------------------------------------------------------------|-------------|

| 2.1<br>2.2<br>2.3 | Basic island-style FPGA structure [14], [15]                                    | 6<br>7<br>8 |

| 2.4               | Optimization of for-statement by loop-unrolling (top) and pilepining (bottom)   | 10          |

| 2.4               | Three types of parallelization                                                  | 11          |

| 3.1               |                                                                                 | 16          |

|                   | Example of system design using Simulink [30]                                    |             |

| 3.2               | The graph of the synthesized hardware [6]                                       | 23          |

| 3.3               | Comparison of tools                                                             | 24          |

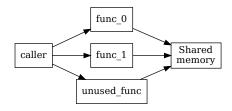

| 4.1               | Structure where data flow is difficult to be modified                           | 27          |

| 4.2               | Flowchart of PDF signal DA conversion                                           | 29          |

| 4.3               | The program of time measurement of mic data processing                          | 29          |

| 4.4               | Measured processing time of mic data processing                                 | 30          |

| 4.5               | Hardware architecture with CoRAM                                                | 30          |

| 4.6               | Arcitecture when data distribution is performed by a module in PL               | 31          |

| 4.7               | System architectrue that PyJer generates                                        | 31          |

| 4.8               | Tool hierarchy                                                                  | 32          |

| 4.9               | Example description of data processing mechanism using Synthesijer              | 32          |

| 4.10              | Example description of sensor data processing using Verilog HDL                 | 35          |

| 4.11              | Example of Top module using Synthesijer                                         | 35          |

| 4.12              | Build flow and tools used for build automation                                  | 36          |

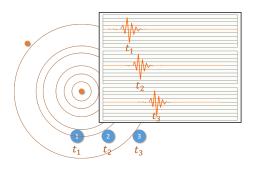

| 4.13              | Position of sound source and its signal                                         | 37          |

| 4.14              | Insertion of delay                                                              | 38          |

| 4.15              | Results of beam-forming                                                         | 40          |

| 4.16              | Utilization of SoC FPGA in IoT/CPS area                                         | 42          |

| 4.17              | Description languages used in PyJer                                             | 42          |

| 4.18              | Comparison of common design and Mulvery architecture                            | 43          |

| 4.19              | Example definition of connections of LIS3DHIF                                   | 47          |

| 4.20              | Target of fluentd                                                               | 50          |

| 4.21              | Mulvery on fluentd                                                              | 50          |

| 4.22              | Schematic diagram of configuration with Mulvery applied to the entire data col- |             |

|                   | lection system                                                                  | 51          |

| 5.1               | Comparison of architecture with MCU-only design and FPGA-based I/O processing   | 53          |

| 5.2               | The synthesizing flow of Mulvery                                                | 55          |

| 5.3  | Software architecture of Mulvery framework                                                |

|------|-------------------------------------------------------------------------------------------|

| 5.4  | Template of MulveryBase class                                                             |

| 5.5  | Example of build_dataflow method                                                          |

| 5.6  | Example of main function and its outputs                                                  |

| 5.7  | Example of counting the number of events using Reactive Programming 58                    |

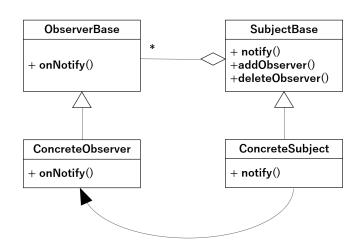

| 5.8  | Class diagram of Observable Pattern                                                       |

| 5.9  | Example of Subject and Observer for mouce events                                          |

| 5.10 | Example description of LINQ on C#                                                         |

| 5.11 | Example of event counting using RxRuby                                                    |

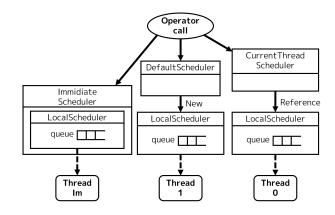

| 5.12 | Relationship among the operators, threads, and principal schedulers 62                    |

| 5.13 | Examples of Scedulers on RxRuby                                                           |

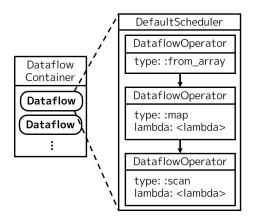

| 5.14 | Structure of a dataflow and its container                                                 |

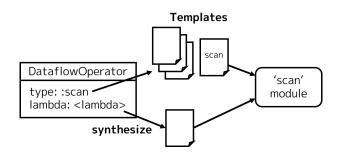

| 5.15 | Workflow that generates the HDL code of a module                                          |

| 5.16 | Example of Observable                                                                     |

| 5.17 | Example of object that synthesizes a lambda abstraction                                   |

| 5.18 | If method on Mulvery                                                                      |

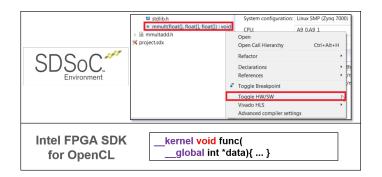

| 5.19 | How to specify hardware offload in SDSoC and Intel FPGA SDK for OpenCL $6^{\prime\prime}$ |

| 5.20 | Example when the location where the method is executed differs between CPU                |

|      | and FPGA depending on how it is called 6                                                  |

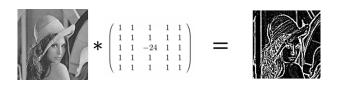

| 5.21 | Applying Laplacian filter                                                                 |

| 5.22 | Example of folding                                                                        |

| 5.23 | Architecture of the program                                                               |

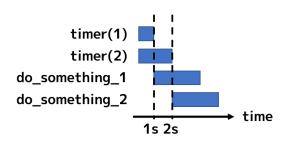

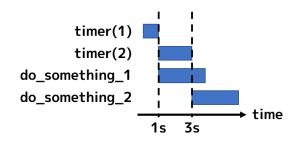

| 5.24 | Pipeline of Fig. 5.22                                                                     |

| 5.25 | Synthesized lambda abstraction in Fig. 5.22                                               |

| 5.26 | Hardware verification using Icarus Verilog                                                |

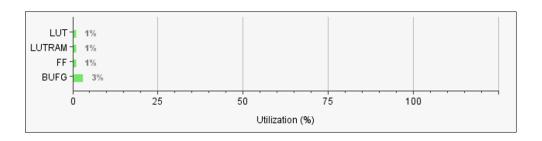

| 5.27 | Resource consumption                                                                      |

| 5.28 | Pseudo code for counting the number of events                                             |

| 5.29 | Architecture with CoRAM                                                                   |

| 5.30 | Data field for NeoPixel [96]                                                              |

| 5.31 | Signal to control NeoPixel [96]                                                           |

| 5.32 | $32 \times 32$ LED matrix                                                                 |

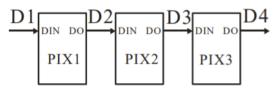

| 5.33 | Serial connection of NeoPixel                                                             |

| 5.34 | Example of build_dataflow to control NexPixel matrix                                      |

| 5.35 | The picture used for the experiment                                                       |

| 5.36 | The NeoPixel showing Fig. 5.35                                                            |

| 6.1  | unsinthesizable pointers                                                                  |

| 6.2  | Examples of indirect call that cannot be resolved by constant folding: (left) A           |

|      | CFG with a condition node, (right) a CFG with two indirect calls                          |

| 6.3  | (top) Naive solution, (bottom) [99]'s solution                                            |

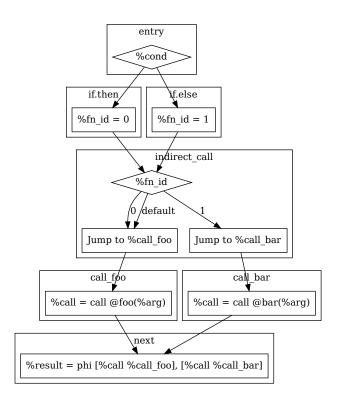

| 6.4  | CFG of Listing 6.3, that contains dynamic indirect function call                          |

| 6.5  | The CFG that the indirect call has removed                                                |

| 6.6  | Indirect call with a multiplexer                                                          |

| 6.7  | Hardware generated from the code including indirect call                                  |

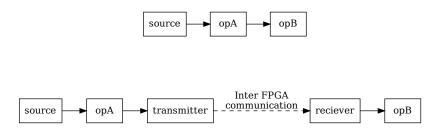

| 7.1  | (top) Original block diagram of source.opA().opB() and (bottom) the program                                    |     |

|------|----------------------------------------------------------------------------------------------------------------|-----|

|      | devided between opA and opB                                                                                    | 91  |

| 7.2  | Usual design method of distributed system which includes FPGAs                                                 | 91  |

| 7.3  | Organization structure of ants                                                                                 | 92  |

| 7.4  | Comparison of response curves with different $\theta_i$                                                        | 94  |

| 7.5  | Graph of $P_{ij}(t)$ using Equation(7.3) $(\bar{T} = 100)$ (upper: $\theta_i = 0.5$ , center: $\theta_i = 1$ , |     |

|      | lower: $\theta_i = 2.0$ )                                                                                      | 95  |

| 7.6  | Flow of Job processing                                                                                         | 96  |

| 7.7  | Network structure for the experiment                                                                           | 99  |

| 7.8  | Number of Workers which is processing task for each 0.1sec of experiment 1                                     |     |

|      | (Upper: a graph when give a Job, Lower: a graph when give two Jobs)                                            | 101 |

| 7.9  | Number of Workers which is processing task for each 0.1sec of experiment 2                                     |     |

|      | (Upper: System-E2A, Lower: System-E2B)                                                                         | 101 |

| 7.10 | A distributed file system and compute nodes                                                                    | 102 |

| 7.11 | Source Code division and assignment computing resources                                                        | 103 |

| 7.12 | An Example of Architecture of PaaS Type IoT data analytics cloud service $$                                    | 103 |

| 7.13 | Numbers of assigned workers for each time (Gray line : 1 stage, Black line : 2                                 |     |

|      | stages, Dotted line: average)                                                                                  | 104 |

# Listings目次

| 3.1  | Description example of a hardware that calculates GCD using Chisel [1] 14  |

|------|----------------------------------------------------------------------------|

| 3.2  | Example of matrix product using Vivado HLS                                 |

| 3.3  | Calculating the average value of an event using Estrel [2]                 |

| 3.4  | Up-down conter by JHDL [3]                                                 |

| 3.5  | Description example of 8-bits up counter using $C\lambda aSH$ [4]          |

| 3.6  | Calculation of $\log_2(N)$ using PyMTL's function-level [5]                |

| 3.7  | Calculation of $\log_2(N)$ using PyMTL's cycle-level                       |

| 3.8  | Calculation of $\log_2(N)$ using PyMTL's register-transfer-level           |

| 3.9  | Example of kernel description using MaxCompiler                            |

| 3.10 | Example of Manager on MaxCompiler [6]                                      |

| 4.1  | Sensor data acquisition in Synthesijer program                             |

| 4.2  | Example of data transfer to DRAM                                           |

| 4.3  | Example of Memory Access Controller                                        |

| 4.4  | TCL script to update IPs for existing Block Design                         |

| 4.5  | Java program for performance measurement                                   |

| 4.6  | Data Processor using Mulvery Core                                          |

| 4.7  | Source code of Fig. 4.6 aftre macro expansion                              |

| 4.8  | Example of Interface on Mulvery Core framework                             |

| 4.9  | Example of Sensor Interface                                                |

| 4.10 | Definition of Sensor Interface that Data Processor uses                    |

| 4.11 | Example of implementation of LIS3DH interface (1)                          |

| 4.12 | Example of implementation of LIS3DH interface (2)                          |

| 4.13 | Example of Data Processor that uses LIS3DH                                 |

| 4.14 | Mulvery language usage example                                             |

| 5.1  | Always statement in Verilog HDL                                            |

| 5.2  | Definition of statement of Mulvery API                                     |

| 5.3  | An implementation of the <i>from_array</i> operator in Mulvery 63          |

| 6.1  | Examples of high-order functions                                           |

| 6.2  | sample list 2                                                              |

| 6.3  | Example with an indirect call                                              |

| 6.4  | Optimized IR of Listing 6.3                                                |

| 6.5  | Three types of store instruction usage regarding function pointers 83      |

| 6.6  | The recursive function to build adjacency graph                            |

| 6.7  | Replacement of the instructions that reference function address/pointer 86 |

| 6.8  | Replacement of an indirect call                                            |

| 6.9  | Map function using void pointer                                            |

| 6.10 | Alternative implementation of map of 6.9 | 87 |

|------|------------------------------------------|----|

| 6.11 | Sample program for the evaluation        | 88 |

# 表目次

| 1.1 | Comparison of standard processor (e.g. CPU, MCU), standard accelerator (e.g.          |    |

|-----|---------------------------------------------------------------------------------------|----|

|     | DSP, GPU), and ASIC (custom circuit)                                                  | 2  |

| 2.1 | The memory table for $f(A, B, C) = (A \& B)   (A \& C) \dots \dots \dots \dots \dots$ | 7  |

| 4.1 | Software-based development environment for mic data processing                        | 28 |

| 4.2 | Platform used for experiment and verification                                         | 37 |

| 4.3 | Zynq-7000 utilization                                                                 | 39 |

| 5.1 | Schedulers implemented on RxRuby                                                      | 62 |

| 5.2 | Classification of Rx operators                                                        | 66 |

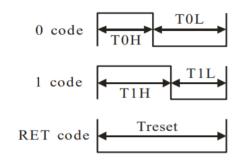

| 5.3 | Signal transmission time length and tolerance [96]                                    | 73 |

| 5.4 | Specifications of the board used in the experiment [97]                               | 74 |

| 5.5 | Software environment used for the experiment                                          | 77 |

| 5.6 | FPGA resource consumption                                                             | 77 |

| 6.1 | FPGA resource consumption (on Cyclone V GX-9)                                         | 88 |

| 6.2 | Performance (simulation)                                                              | 89 |

| 7.1 | Computers used for the experiment                                                     | 99 |

# 第1章 緒論

## 1.1 ハードウェアによるソフトウェアの高速化

#### 1.1.1 ハードウェアアクセラレーション

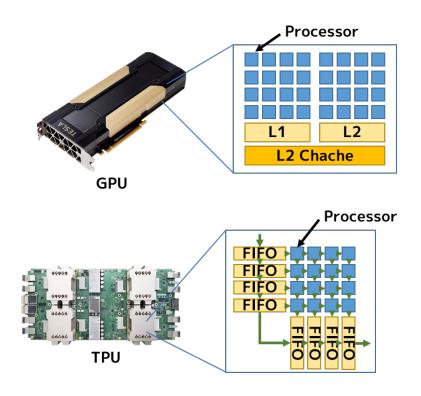

ムーアの法則の終焉によって,ソフトウェアの性能向上は限界を迎えつつある[7]. CPU のよ うな汎用的なプロセッサはプリミティブな命令を組み合わせて処理を行うが,ハードウェアアク セラレータ (hardware accelerator) と呼ばれるデバイスを目的に合わせて用いることでシステ ム全体の処理性能を向上させることができる.このようにハードウェアアクセラレータを用いた 処理の高速化をハードウェアアクセラレーション (hardware acceleration) と呼ぶ.このよう なアクセラレータには特定の処理に特化した LSI (large-scale integration) が搭載されており,動 画のエンコーダ・デコーダといった機能単位のアクセラレータや , DSP (digital signal processor) のようなディジタル信号処理に特化したプログラマブルデバイスなど , 様々な粒度のアクセラレー タが存在する.一般消費者にも広く利用されているハードウェアアクセラレータとしては,主に コンピュータグラフィクスやゲームの描画処理に利用される GPU (graphics processing unit) が 知られている. 浮動小数の処理に必要な機能を具えた比較的単純な PE (processing element) を数 百~数千個並べ高い並列度で処理を行うことで高い処理性能を実現している(図 1.1 上 ). 浮動小 数演算は科学分野や機械学習,人工知能の分野でも多く利用されるため,コンピュータグラフィ クス以外の分野に GPU を応用する GPGPU (general-purpose GPU) も広く行われている [8].こ のようなデバイスでは,機能を特化させるほど電力性能や処理速度が向上するが,用途が限定的 となり製造数も汎用的なものと比べて少なくなるため、相対的に開発製造のコストが大きくなり 価格も上昇するといったトレードオフがある.

家庭用の電子機器やモバイルデバイスの開発などさらに高い電力性能が要求される場面においては個々のシステムに合わせて設計されるカスタム IC (application specific integrated circuit; ASIC) が利用される.身近な例としては,デジタルカメラの画像補正や,テレビや動画プレーヤーなどで利用される専用の動画エンコーダ/デコーダなどが挙げられる.人工知能分野,特に深層学習(deep learning)においてはベクトルやテンソルの演算を繰り返し行うため,Google が TPU (Tensor Processing Unit) と呼ばれる高性能な計算を実現するためのハードウェアアクセラレータを発表している [9].多数の PE を並べた点は GPU と共通であるが,TPU の場合には隣接する PE が接続(図 1.1 下)され PE 間で心臓の収縮(Systolic)のようにデータを転送し処理を行う特徴を持つ.このようなアーキテクチャは H.T.Kung らが提案したシストリックアレイ(systoric array)として知られており [10],これを応用して高いスループットでテンソル演算を行うアルゴリズムが知られている $^1$ .

特定のアプリケーション専用に LSI を開発する ASIC は最も設計の自由度が高く目的に応じて制作するものであるため性能の追及が可能であるが、開発と製造にかかるコストや納品までにかかるターンアラウンドタイム (turn around time) が非常に大きくなってしまう、表 1.1 に,CPU

$<sup>^1</sup>$ シストリックアレイを応用したアルゴリズムはシストリックアルゴリズム  $(systoric\ algorithm)$  として多くの研究がなされている [11].

☑ 1.1: The architecture of tipical GPU and TPU

表 1.1: Comparison of standard processor (e.g. CPU, MCU), standard accelerator (e.g. DSP, GPU), and ASIC (custom circuit)

|        |   | Performance             | Flexibility           | Cost                    |

|--------|---|-------------------------|-----------------------|-------------------------|

| Better | 1 | ASIC                    | Standard<br>processor | Standard<br>processor   |

|        | 2 | Standard<br>accelerator | Standard accelerator  | Standard<br>accelerator |

| Worse  | 3 | Standard<br>processor   | ASIC                  | ASIC                    |

や MCU といった量産されている標準的なプロセッサ (表中 standard processor) , DSP や GPU のような標準的なアクセラレータ (表中 standard accelerator) , ASIC の特徴を比較形式でまとめる . ASIC は処理能力や電力性能について最も優れているものの , 他のシステムに利用する柔軟さや開発コスト , 価格といったコスト面では汎用品と比較して不利である .

#### 1.1.2 FPGA を用いたアクセラレーション

カスタム回路を利用したいが量産しないためコストが見合わない,システムや技術の更新が頻繁でターンアラウンドタイムを長く取れない,といった場面においては,再構成可能コンピューティング(reconfigurable computing)が有効である [12] .  $\mathbf{FPGA}$  (field-programmable gate array) に代表される,目的によってアーキテクチャの構成をカスタマイズできる再構成可能デバイス(reconfigurable device)を利用しシステムに応じた専用アクセラレータを開発する. $\mathbf{FPGA}$  も LSI の一種であるが,エンドユーザが設計したカスタムディジタル回路を書き込むことができるため,再構成可能デバイスと呼ばれている. $\mathbf{FPGA}$  は,同じ回路が動作する ASIC と比較する

と動作クロック周波数が低く性能が劣るという問題があるものの,製造コストやターンアラウンドタイムを大きく節約しながらも専用アクセラレータや専用プロセッサを構成することが可能であるといった利点がある.

今後 FPGA を用いた高性能計算 (High Performance Computing; HPC) の需要が増しさらなる 設計開発コストの増大が見込まれており [13],カスタム回路設計の生産性を向上させるための研究が盛んに行われ,様々なツールが開発されている.

## 1.2 ディジタル回路設計の現状と課題

#### 1.2.1 ハードウェア記述言語を用いたディジタル回路設計

ASICやFPGAで用いるディジタル回路の設計は、ハードウェア記述言語(hardware description language; HDL)を用いたレジスタ転送レベル(Resister Transfer Level; RTL)による開発が必要となる。しかしながら HDL による設計はクロックサイクルレベルの低い抽象度の記述が必要であり、高性能なカスタム回路の設計が可能な反面、開発にかかるコストや time-to-market が大きくなってしまう問題がある.

記述の性質から HDL はバグが発生しやすく、デバッグにも様々なツールが必要で熟練した技術が必要である.対してソフトウェア開発はデバッグや解析手法が深く研究され知見が広く共有されていることが特徴であり、ハードウェア設計と比較して開発コストが低く生産性が高いといえる.加えて、ソフトウェア開発ではより多くのツールが利用可能であり、オープンソースソフトウェアやフリーウェアなど入手性の高いツールも数多い.このことから、ASIC の設計や FPGAを用いたシステム開発はコストが高く、電力性能や計算速度の利点にも関わらず利用できる場面は限られている.

#### 1.2.2 ディジタル回路設計の生産性を高めるためのアプローチ

これらの問題を解決するため,大きく二つのアプローチが知られている.ひとつ目はメタプログラミングである.これを用いたツールは DSL (domain specific language) やマクロなどを用いて回路を記述し,HDL を生成する.これによって,HDL と比較してハードウェアの記述量を大きく削減することができ,記述の抽象度を向上させることができる.これらのツールは既存のプログラミング言語を用いた記述である場合もあるが,以前として回路設計の知識や技術を必要とするため,生産性を高めることが可能ではあっても設計のコストは依然として高いままである.

ふたつ目のアプローチは高位合成 (high-level synthesis; HLS) である.HLS は,C/C++や Java といったプログラミング言語によって記述されたプログラムやアルゴリズムと同じふるまいをする回路を合成する技術である.既に様々な言語による HLS ツールが開発されている.FPGA の大手ベンダである Xilinx や Intel は C 言語ベースのツールを公開しており,利用可能である.一般にこれらの HLS ツールは既存のソフトウェアの高速化を意図して設計されており,プログラムの一部を FPGA にオフロードする形で利用することが想定されている.しかしながら,エンドユーザはいくらかのアノテーションをプログラムに書き加える必要がある.これはソフトウェアの記述と回路記述のパラダイムが大きく異なり回路の合成に必要な情報が十分に含まれていないことが原因である.プログラミング言語はコントロールフロー型の記述であり,HDL はデータフロー型の記述である.これは二つの問題を引き起こす.第一に,ソフトウェアのプログラムには並列性の記述に関する情報が含まれていないため,並列プログラミングで用いるような記述が必要となる.第二に,データフローに関する情報が含まれていないため,自動的なパイプライン化が難し

く,最適化のための情報を付け加えなければスループットが非常に低くなってしまうことや,複雑で巨大なステートマシンが生成されてしまう問題がある.

PCIe などのインタフェースを介した拡張カードを利用する場合や単一のチップに搭載した SoC FPGA (system-on-chip) のように, CPU と FPGA が共存した計算機がしばしば用いられるため, ソフトウェアとハードウェアを同時に開発するコデザイン (co-design) 環境も広く用いられている.このようなコデザイン環境においても高位合成が利用されるが, コデザイン環境は CPU と FPGA の通信の記述コストを削減することが主な役割であり, ハードウェア部分の設計について は高位合成の抱える問題が依然残されている.

システムの素早い開発のため、ソフトウェアの分野ではPythonやRubyといった軽量言語 (lightweight language; LL) がしばしば用いられる.このような言語は動的型付けを応用した拡張性の高い型システムを用いることで開発効率と高い再利用性を実現していることが特徴として挙げられる.ハードウェア開発においては、これらの言語のように開発効率に主眼を置いたツールは研究が進んでおらず、発展の余地が残されているといえる.

## 1.3 研究目的と本稿の構成

このような背景から,本研究では,ソフトウェア開発の分野で生産性を高めるために用いられているプログラミングモデルによってディジタル回路設計の生産性を高めることが可能か?という問いに取り組んだ.FPGA を主なターゲットとして,ディジタル回路設計の生産性を高めるための技術についての研究を行った.本研究は大きく分けて1)フレームワークを用いた最適なアーキテクチャの自動生成ツールの研究,2)ディジタル回路設計に近いプログラミングパラダイムを用いた回路設計ツールの研究の二つのアプローチに分けられる.

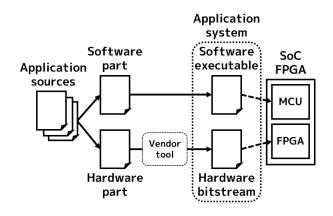

3章では、既存のディジタル回路設計支援ツールに関する文献調査と本研究の立ち位置について議論する、4章では、電力効率が重要である IoT/CPS (Internet-of-Things, cyber-phisical system) の分野のための開発環境の研究について説明する、エッジデバイス開発に適したアーキテクチャを構成するためのフレームワークを開発し、エッジデバイスに合った既存のツールや最適化手法を自動的に適用することで、回路設計の専門家でない開発者でも高いパフォーマンスを発揮するシステムを開発した、5章では、ハードウェア設計言語と近いパラダイムを持つプログラミングモデルを用いて記述したプログラムからディジタル回路を合成するための手法についての研究について述べる、筆者は提案手法を応用しハードウェア・ソフトウェアコデザイン環境 Mulvery を開発し、その評価を行った、6章では、HLS ツールにおいてサポートされないことがほとんどである関数ポインタの実現のための手法について説明する、関数ポインタをサポートすることによって高階関数などの抽象化のためのテクニックが利用できるようになる、C 言語ベースの高位合成ツールにおいてこれまで実現が困難とされていた関数ポインタを実現手法について説明し、関数ポインタが高位合成にもたらす効果や利益について議論する、続く7章では、FPGAを含むヘテロジニアス計算機環境において Mulveryを分散コンピューティングに応用する手法について述べる、そして最後の8章で研究全体の総括を行う、

# 第2章 FPGAの原理と回路設計の技術

本研究では,FPGA を主なターゲットとしたディジタル回路設計の技術に関する研究を行う. 具体的な研究内容に触れる前に,FPGA を用いたシステム開発と技術の現状について深く理解するため,この章でFPGA の基本的な原理について説明する.また,本研究と密接に関連しているプログラミング言語を用いて回路を設計するツールの基本的な原理について説明する.

# 2.1 FPGA の技術の概要

### 2.1.1 FPGA の原理

#### FPGA の構造

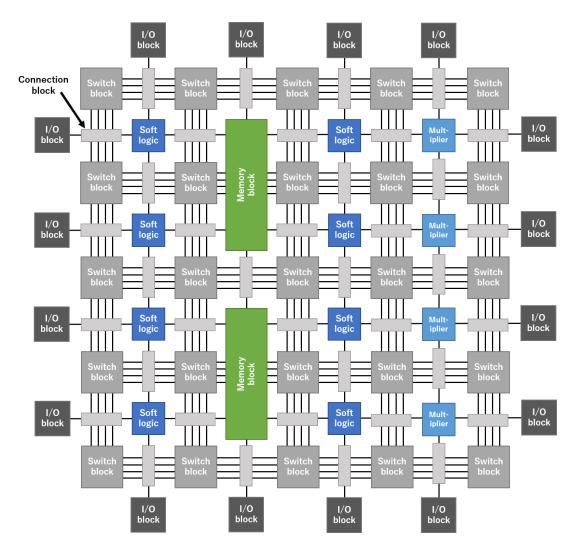

図 2.1 に , 現在の多くの FPGA が採用しているアイランドスタイル FPGA と呼ばれる種類の FPGA の概略図を示す [14] . FPGA は , 大きく分けて

- 汎用ロジック (soft logic),

- 配線要素 (switch block, connection block),

- 入出力ブロック (I/O block),

- 専用ロジック (memory block and multiplier)

の四種類の要素で構成される.汎用ロジック(general logic, soft logic)は論理回路を構成するプログラマブルなブロックであり,配線要素はブロックを接続するためのプログラマブルなブロックである.入出力ブロック(I/O block)は外部への I/O を提供するブロックであり,これもプログラマブルである.そして専用ロジックは図中のメモリブロック(memory block)や乗算器(multiplier)など専用に実装されたブロックである.メモリや乗算器は汎用ブロックの組み合わせでも実現可能であるが,多数のブロックを消費する上に非常に多く用いられるため専用のブロックを用意することで回路面積の節約と処理の高速化に貢献する.汎用ロジックと専用ロジックを対比させて,それぞれ soft logic, hard logic と呼ばれることもある [14].

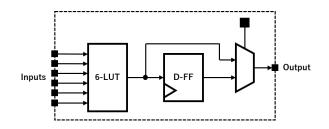

### 論理要素と論理クラスタ

汎用ロジックのブロックは図 2.2 に示すような basic logic element (BLE) によって構成される.BLE は主に loop-up table (LUT), D-フリップフロップ (D-FF) で構成され,k ビットの入力に対して 1 ビットの値を出力する.図 2.2 は,6 入力 1 出力の BLE である.LUT は一般には k ビット入力 1 ビット出力のメモリテーブルである.このようなメモリは真理値表の代わりに用いることができ,k 入力のメモリは k 個の変数を持つ任意の論理関数( $2^{2^k}$  種類)を表現することができる.たとえば論理関数 f(A,B,C)=(A&B)|(A&C) に対応する 3 入力 LUT のメモリテーブルは表 2.1

☑ 2.1: Basic island-style FPGA structure [14], [15]

☑ 2.2: Basic logic element (BLE) [16]

表 2.1: The memory table for f(A, B, C) = (A & B) | (A & C)

| Address | Data | Address | Data |

|---------|------|---------|------|

| 000     | 0    | 100     | 0    |

| 001     | 0    | 101     | 0    |

| 010     | 0    | 110     | 1    |

| 011     | 1    | 111     | 1    |

に示すものとなる.変数の数がkよりも多い論理関数を表現する場合には複数の論理関数に分解して,複数の BLE を組み合わせて表現する.LUT の入力数kが大きいほど複雑な論理関数(変数の多い論理関数)を表現できるため,ある論理回路を構成するために必要な BLE の数を減らすことができ,面積や伝送遅延の点で有利になる予測ができる.しかしながら必要になるメモリのサイズは  $2^k$  と指数的に増加し結果的に必要な配線の量も増えるため,面積あたりに実装できる BLE の数が減少するというトレードオフがある.文献 [16] によれば,LUT の入力が 5,6 の場合に面積と遅延の面で良好なパフォーマンスが得られるとされ,実際に近年の FPGA の多くで 6 入力 LUT が採用されている.

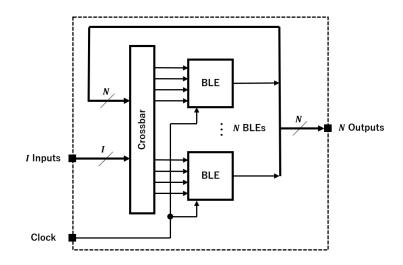

入力信号は複数の BLE で共有できることが知られており , 図 2.3 のように複数の BLE をまとめた 論理クラスタ (logic cluster) を構成することで面積や速度の性能を改善することができる . 文献 [16] では , 論理ブロックの使用効率が最適になるようなパラメータ設定について , 論理クラスタの入力信号の数 I と LUT の入力信号数を k , 論理クラスタに含まれる BLE の数を N として

$$I = \frac{k}{2}(N+1) \tag{2.1}$$

と実験を通して定式化している.論理クラスタを用いない場合には  $I=k\times N$  であるから,一方で LUT の場合と同様に入力数や BLE の数が増えるにつれ論理クラスタ内での伝送遅延が大きくなるトレードオフがあり,文献 [16] では N が  $4\sim 10$  かつ k が  $4\sim 6$  で面積あたりの遅延について最も良い結果が出ることを報告している.

#### 2.1.2 FPGA の EDA 技術

RTL 記述から FPGA に書き込むことができるファイルを生成するためには electric design automation (EDA) ツールが必須であり , FPGA で実行する回路の性能にとって非常に重要な役割を果たす . FPGA に書き込むことができるファイルはビットストリームと呼ばれ , Verilog HDL や VHDL などの HDL による RTL 記述からビットストリームを生成するまでには , 次のような処理を経る :

1. 論理合成 (logic synthesis)

**図** 2.3: Logic cluster [16]

- 2. テクノロジーマッピング (technology mapping)

- 3. クラスタリング (clustering)

- 4. 配置 (place)

- 5. 配線 (route)

- 6. ビットストリーム生成 (generate bitstream)

論理合成 は、RTL 記述からゲートレベルの論理回路 $^1$ に変換する工程である.この際に EDA ツールは論理回路の不要な配線の削除や最適化などを行っていく.

テクノロジーマッピング では,論理回路で使われているゲートの代わりに FPGA の論理セルを用いた回路に変換する工程である.例えば UCLA(University of California, Los Angeles)の研究グループが提案した FlowMap [17] ではブーリアンネットワークで表現された有向グラフ(DAG)において k-入力となるようにカットを加えていき,k-入力 LUT に対応させていく(mapping)といった流れで処理を行う.

クラスタリング では,LUT レベルの回路において LUT をクラスタリングし,論理クラスタをマッピングしていく工程である.論理クラスタ内の配線は論理クラスタ間の配線と比較して高速であるため,単に論理クラスタに多くの LUT を詰め込むのみならず,論理クラスタ間の接続をなるべく短く少ない接続に抑えることも高いパフォーマンスを発揮する回路を合成するにあたって重要な目標となる.

配置配線 では,論理クラスタレベルの回路において各論理クラスタを FPGA 上の物理的な位置に配置し,その配線を確定させていく作業である.実際の処理では配置と配線は別々の工程として行われるが,しばしば配置配線 (place and route) とひとまとまりにして呼ばれる.論理クラスタは 2 次元上に整列しているため,回路中の論理クラスタ  $C_1, ... C_n$  と FPGA 上にある利用可能な論理クラスタ  $T_1, ..., T_n$  に対して回路中の論理クラスタ  $C_i, C_k$  間のバス幅が  $w_{ik}$ ,利用可能な

<sup>1</sup>ゲート回路, ネットリストなどともよばれる

論理クラスタ  $T_j,T_l$  の間の距離が  $d_{jl}$  であるとしたとき, $C_i$  を  $T_j$  に設置したときに 1 ,それ以外で 0 になる変数  $x_{ij}$  によって,論理クラスタの配置は次の目的関数の最小化問題と考えることができる:

$$\sum_{i,j,k,l=1}^{n} w_{ik} d_{jl} x_{ij} x_{kl}. \tag{2.2}$$

これは二次割当問題 (quadratic assignment problem; QAP) そのものであり,よって計算複雑性 クラスが NP-hard に相当するような問題である.また配線では,グラフ上で最短経路探索を行い 概略配線を行った後,複数のバスが同じ経路を使うことによる混線を避けるため競合ワイヤにコストをかけ,改めて経路探索を行う.これを競合がなくなるまで繰り返していき,詳細配線を決定する [15].このように配置配線においては複数の計算量の大きな最適化問題を解く必要があり,回路規模が大きくなるにつれ指数的なオーダーで処理に時間を要するようになることがわかる.

ビットストリーム生成 では, FPGA 内の LUT やデータバススイッチの設定を生成し, FPGA に書き込むことができるファイルを生成する工程である.

#### 2.1.3 参考文献

FPGA のデバイスに関する技術については ,I. Kuon らによる FPGA Architecture: Survey and Challanges [14] に詳細にまとめられている . 日本語で読むことのできる文献としては , 天野らによる FPGA の原理と構成 [15] が非常に参考になった .

# 2.2 高位合成の原理

#### 2.2.1 高位合成の概要と利点

ディジタル回路設計は一般的には HDL を用いて行われるが , 近年では C や Java などの高級言語 (high-level language; HLL) から RTL 設計を合成する回路設計も行われるようになっている . このような設計は高位合成 (high-level synthesis; HLS) と呼ばれており , Xilinx や Intel などの大手ベンダからも HLS ツールが提供され実用的な段階に入ってきている .

RTL 設計は設計に時間がかかる上にミスの混入も発生しやすく,またコードの再利用性もあまり高くないために開発効率が非常に悪い.また,RTL 設計を検証するためにはシミュレーションを行う必要があるが,RTL シミュレーションは各レジスタの値などを全てシミュレーションしなければならないため,非常に低速である.対して HLS を使う場合,RTL シミュレーションを行う前にプログラムをそのまま実行してシミュレーションの代わりとするビヘイビアシミュレーションが可能となり,シミュレーションに必要な時間を削減し検証のコストを大幅に低減することができる.また抽象度の高さや設計のしやすさなどから開発効率も格段に改善する.

#### 2.2.2 動作合成

多くの  $\operatorname{HLS}$  ツールでは  $\operatorname{C}$  言語や  $\operatorname{C}$  言語をベースとした独自の言語を用いているため,この節では入力を  $\operatorname{C}$  言語であるとして説明する. $\operatorname{HLS}$  ツールはまず,入力されたプログラムの制御フローグラフ (control flow graph; CFG) とデータフローグラフ (data flow grpah; DFG) を生成する.その後,

2.4: Optimization of for-statement by loop-unrolling (top) and pilepining (bottom)

- アロケーション (allocation)

- スケジューリング (scheduling)

- バインディング (binding)

#### の3つの工程を行う.

アロケーション の工程では,プログラムが必要としているメモリや DSP などのコンポーネントを解析し確保する作業を行う.FPGA では BRAM と呼ばれるオンチップメモリが多数配置されているため,プログラム全体で共通のメモリを使うよりも,依存関係がない部分を細かく切り分けてそれぞれで使用する方が遅延やデータ幅の観点で有利であり,高速化に寄与する.しかしながら,データ間の依存関係のプログラムから最大限の最適化結果を得られるような解析を行うことは難しいため,人間の手によって指示を与え HLS ツールの推論を手助けする必要がある.

スケジューリング では,CFG をもとにして処理の流れをステートマシンに変換していく.ディジタル回路ではすべての順序回路や組み合わせ回路のモジュールが並列に動作するため,CFG,DFG を用いて,実行順序やモジュール間のタイミングを合わせる処理が必要となる.この場合にも,C言語(やその他のプログラミング言語)ではデータや制御の依存関係の表現が不十分な場合があり,人間の手で情報を付け加え最適化を促す必要がある.図 2.4 に for 文についてのスケジューリングの例を示した.配列に対し逐次処理を行うようなループを展開(loop unrolling)することで配列の全ての要素に対してまとめて処理を実行することができるようになる場合がある.一方で,ループ展開するのではなく処理をパイプライン化することでメモリからデータを読み出し次第即座に処理を開始し,スループットを高める最適化も考えられる.単純なループではどちらが最適化判断できることもあるが,複雑なループやデータ構造である場合にはこれらの自動的な解決は難しく,ユーザが最適化を施す必要がある.パイプライン化などの並列化のテクニックについては次節でより詳細に説明する.FPGA 上の BRAM には 1 クロックでアクセス可能なバスの数に制限があるため,設計者はこのような点も踏まえてアロケーションとスケジューリングが意図通りに行われるようなプログラムを記述する必要がある.

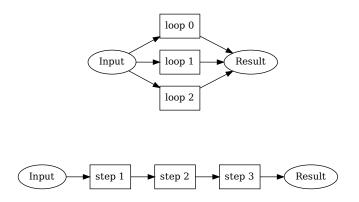

**図** 2.5: Three types of parallelization

バインディング バインディングでは,アロケーションで確保した FPGA 上の資源を実際に割り当てていく作業である.より多くのメモリブロックや浮動小数点演算器を割り当てたパートは計算の並列度が高まり処理が高速になるが,すべてのパートでそのようなバインディングを行うとリソースが不足してしまう.このようなリソース割り当てにおいても C 言語の表現力のみでは解析が難しいため,やはり人手による指示やコードの最適化が必要である.

#### 2.2.3 参考文献

数多くの高位合成ツールや回路設計ツールの比較が、M. W. Numan らによる Towards Automatic High-Level Code Deployment on Reconfigurable Platforms: A Survey of High-Level Synthesis Tools and Toolchains [18] にまとめられている.

## 2.3 高速化技法

この節では,ハードウェアアクセラレーションで用いられる技法の中でも,特に HLS を用いた 回路設計において特に重要となる高速化技法について簡単に説明する.システムにデータを入力 してから処理結果が出力されるまでの時間をレイテンシ,一定の時間中に入力することができる データの量を「スループット」と呼ぶ.

#### 2.3.1 並行計算

複数の処理を並行に実行する技法として,作業をいくつかのステップに分けそれぞれ別のリソースで計算するパイプライン化と,ある作業中で互いに依存関係のない部分を並列化するものの大きく二種類に分けて説明できる.

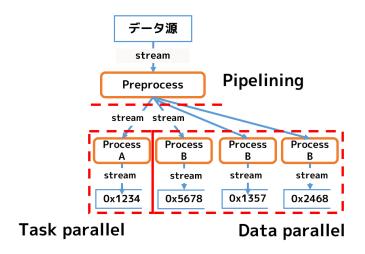

#### パイプライン化

図 2.5 中で Pipelining で示した分割は ,処理の流れを前後に大きく二分している.図中「Process」で示したブロックは ,処理が完了するとデータは次の「Process A/B」のブロックに引き継ぐことで空いたリソースとなり ,データ源から新たなデータを取り出して次のデータの処理を開始することができる.すなわち ,データが処理されるまでのレイテンシは変化しないものの ,計算リソースを効率的に利用し単位時間により多くのデータを投入することができるようになるため , スループットを向上させることができる.

#### 処理の並列化

対して処理の並列化は,レイテンシを短くするための技法である.並列化はさらに二種類に分類することができる.

タスク並列化 たとえば  $a = processA(in0, in1); b = processB(in0, in1); という処理 においては, <math>a \ge b$  の計算の間に依存関係がないため, すなわちデータである in0, in1 を受け取った時点で並列に処理を開始しても問題がない. このような並列化はタスク並列化 (Task parallelization) と呼ばれる.

データ並列化 for (data in array) result += processB(data) といったように配列からデータを逐次取り出して処理する例を考える.この場合,あるデータは他のデータとの依存関係がないため,関数 process を実行するリソースを複数用意すれば,その分並列に動作させることができる.つまり,配列の0番目から99番目の要素を担当する回路,100番目から199番目を担当する回路・・・といったように複数のリソースで分担することで処理を高速化することができる.このような並列化はデータ並列化 (Task parallelization) と呼ばれる.

### 2.4 まとめ

この章では、FPGAの原理とFPGAの回路設計で用いられているEDA技術についての概要をまとめた。また、プログラムからハードウェアを合成するHLSの原理の概要も説明した。本研究では、特にHLSにおいて課題とされている「人手による指示やコードの最適化」について取り組む。この章で説明した通り、人手による指示やコードの最適化はプログラムの中に回路合成に必要な情報が十分に含まれていないことが根本的な原因であり、何かしらの形で情報を与える以外に、今後のコンパイラ技術やHLS技術の進展によって改善するのは難しい。本研究では、このような不十分な情報をいかに補うかという点に着目し、研究を進めていく。

# 第3章 関連研究

#### 3.1 はじめに

#### 3.1.1 ソフトウェア開発の技術の有効活用

ソフトウェア開発の世界では,生産性を高めるための開発手順やプログラミング手法などがよく研究されており,多くのカスタム回路設計ツールにおいてもハードウェア開発にこれらの手法を取り入れることを目指している.近年,システムに求められる真の要件を見出すため,リリースまでの期間の短縮とテストの繰り返しを重要視した開発手順やプログラミング手法が注目を集めている.

ソフトウェア開発の開発手順とハードウェア開発 生産性を高めるための開発手順の例として,アジャイルソフトウェア開発フレームワーク [19] が挙げられる.この開発手順では,要求に答えたシステムをできるだけ素早く開発し,評価する手法である.さらに開発と評価を継続的に繰り返すことでシステムの完成度を高めていく.この開発手順は,開発初期には全体像が明確化されず最終的な開発期間が延びる可能性がある反面,テストまでの期間が短く,ユーザの要求やシステム要件の見直しを何度も行うことが可能でありユーザの要求に正確に応えることができるメリットがある.

ASIC や VLSI の開発では莫大な製造コストがかかるため,このような手法は取り入れられてこなかった.しかしながら FPGA を用いたシステムではカスタム回路を何度も修正することができるため,このようなソフトウェア開発手法と同様の開発の技術を取り入れることができる.

ソフトウェア開発のプログラミングモデルとハードウェア開発 生産性を高めるプログラミング 手法の例として,軽量言語 (lightweight language; LL) [20] を用いたプログラミングが挙げられる.動的型付けやラムダ抽象の採用など記述の抽象度を高めるものが多く,高い生産性から様々 な場面で利用されている.IEEE の 2017 年の記事では,Python が最も人気の言語であるとされている [21].Python は機械学習や深層学習のシーンで多く利用されており,ハードウェアアクセラレーションの対象としても重要なターゲットである.

FPGA 上ではアプリケーション実行中にバス幅や信号の経路を動的に変更するのは困難である.しかしながら軽量言語には動的プログラミング言語が多く,デジタル回路を合成する際に静的に型情報や呼び出される手続き(メソッド)が決定できないため,カスタム回路設計ツールに利用される例は少ない.

また,型システム [22] を用いた型検証によって記述の正当性を検証する研究も多く行われている.回路設計では,信号線の接続でバス幅が異なると意図しない動作が起こりバグの温床となるため,型安全な言語を使うことによって不正な信号線の接続を回避することができる.

Listing 3.1: Description example of a hardware that calculates GCD using Chisel [1]

```

1 class GCD extends Module {

val io = IO(new Bundle \cdot

val a = Input(UInt(16.W))

3

val b = Input(UInt(16.W))

4

val e = Input(Bool())

5

val z = Output(UInt(16.W))

val v = Output(Bool())

7

})

8

val x = Reg(UInt())

9

val y = Reg(UInt())

10

when (x > y) \{ x := x - y \}

11

.elsewhen (x \le y) \{ y := y - x \}

12

when (io.e) \{ x := io.a; y := io.b \}

13

io.z := x

14

io.v := y === 0.U

15

16 }

```

#### 3.1.2 動向調査の意義

カスタム回路設計支援ツールは、様々な動機から設計がなされている。例えば、ハードウェア技術者が記述の手間を省くため、特定のアプリケーションに特化させデジタル回路設計の知識を不要にするため、などの理由がある。本研究では、デジタル回路設計の知識を持たないプログラマが FPGA を利用して高い処理能力や電力性能を実現するためのツールの研究・開発を行う、デジタル回路設計の知識を前提としないカスタム回路の設計かつ高い性能を発揮する回路の合成を目指すことを試みる。

そこで,これまでに発表されてきたカスタム回路設計ツールについて調査・分析し,本研究の立ち位置を明確にすることで,これまでの研究と全く異なる新しい試みであることを確かめることを目的とする.

### 3.2 カスタム回路設計ツールの種別

HDL 記述よりも高い生産性を実現するため設計されたカスタム回路設計ツールは三種別に分類することができる.この節では,代表的なツールを例に挙げながら,それぞれの種別について説明する.

#### 3.2.1 ドメイン特化言語を用いたレジスタ転送レベル設計

第一は, HDL を効率よく記述するためのドメイン特化型言語 (Domain Specific Language; DSL) を用いた RTL 設計ツールである. 以降, DSL ベースの RTL 設計ツールと呼ぶ.

Verilog HDL や VHDL の生産性の低さの一因は,記述の低い抽象度にある.アプリケーションに応じて入出力バスなどのインタフェースは変化するが,このような差分を言語仕様のレベルで吸収できず,都度 Wrapper を実装したりモジュールの再設計を行う必要がある.そこで,モジュールや入出力の抽象度を高める型システムやプログラミングパラダイムを導入した言語を用いて RTL設計が可能となるツールが提案されている.

この種類の代表的なツールである Chisel[23] のコード例を Listing 3.1 に示す . Scala を用いて記述されているが , 記述の内容は Verilog や VHDL と同様に RTL の記述であることがわかる .

```

#pragma HLS ARRAY_RESHAPE variable=a complete dim=2

#pragma HLS ARRAY_RESHAPE variable=b complete dim=1

2

3

for (int i = 0; i < MAT\_A\_ROWS; i++){

4

#pragma HLS PIPELINE

5

for (int j = 0; j < MAT_B\_COLS; j++){

6

res[i][j] = 0;

7

#pragma HLS PIPELINE

8

for (int k = 0; k < MAT_BROWS; k++)\{

res[i][j] += a[i][k] * b[k][j];

9

10

11

12

}

13

```

#### 3.2.2 汎用プログラミング言語や DSL を用いた動作レベル設計

第二は,C/C++言語や Java 言語などの汎用プログラミング言語(General Programming Language; GPL)や DSL を用いた動作レベル設計である.このようなツールを実現する技術 は高位合成 (high level synthesis; HLS) として知られまとめられている [24].以降は HLS ツールと呼ぶ.

計算に用いられるアルゴリズムはしばしば手続きとして定義される.しかし RTL 設計ではデータフローモデル [25] で記述する必要があり,アルゴリズムが複雑であるほど大きな開発コストを要してしまう問題があった.そこで GPL で記述されたアルゴリズムを解釈し同じふるまいが実装されたデジタル回路を自動的に設計する HLS ツールが数多く提案され [26], [27],商用利用も行われている [28].

この種類の代表的なツールである Vivado HLS [23] のコード例を Listing 3.2 に示す.このコード例では,三重ループによる行列演算の記述に対して最適化が行われている.記述のパイプライン化のようなアーキテクチャの制御 (5, 8 行目のプリプロセッサ命令) のほか,配列がメモリ上にどのように配置されるかの制御 (1, 2 行目の命令) を行っている.

#### 3.2.3 ドメイン特化言語を用いたシステムレベル設計

第三は  $\mathbf{GUI}$  や  $\mathbf{DSL}$  を用いたシステムレベル設計である.以降,システムレベル設計ツールと呼ぶ. $\mathbf{DSL}$  ベースの  $\mathbf{RTL}$  設計ツールとよく似ているが,より特定のドメインに特化させることで  $\mathbf{RTL}$  設計を必要としないものや,既に用意されたモジュールを組み合わせることで  $\mathbf{RTL}$  設計をせず簡単にカスタム回路を設計するためのツールを指す.

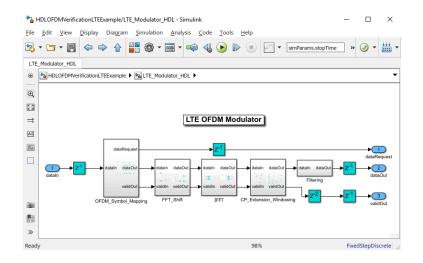

ハードウェアの関連する組込みシステムのモデルベース開発と相性がよく,MATLAB/Simlink [29], [30] において,HDL Coder としてハードウェア設計ツールが実現されている.Simulink での GUI 設計の例を図 3.1 に示す.このように GUI や DSL を用いてコンポーネントを組み合わせたデータから,FPGA や ASIC の回路として合成可能な HDL 記述を自動的に合成することができる.

#### 3.3 既存の開発ツールの分類と特徴

この節では,これまでに発表されているカスタム回路設計ツール 18 種について,2 節で説明した三種別に従って分類し,それぞれの特徴についてまとめる.ツール名に付した年は,そのツー

☑ 3.1: Example of system design using Simulink [30]

Listing 3.3: Calculating the average value of an event using Estrel [2]

```

module AVERAGE:

# declare part

2

3

input INCREMENT_AVERAGE(integer);

output AVERAGE_VALUE(integer);

4

# body

ver TOTAL := 0: integer, NUMBER := 0: integer in # declare local variables

7

every immediate INCRÉMENT_AVERAGE do

TOTAL := TOTAL + ? INCREMENT\_AVERAGE;

9

NUMBER := NUMBER + 1;

10

emit AVERAGE_VALUE(TOTAL / NUMBER) # emit signal to output port

11

12

end

13

end.

```

ルに関する最も古い論文もしくはツール自体が公開された年を示す.

#### 3.3.1 DSL ベースの RTL 設計ツール

Esterel (1992) Esterel[2] は,リアクティブシステムを記述するために設計された平行プログラミング言語である.リアクティブシステムとは,入力イベントに対し,あらかじめ決められた手続きを適用して出力するようなシステムである.Estrel は,異なる入力イベントはコンカレントに処理されるという思想に基づいており,入力イベント毎に新しいサブプロセスが起動する.インタフェースの変数間の関係(同時に到着する/関係がない)を表す記法を言語仕様として持ち,コンパイラはより正確な決定性状態機械を構築し最適化を施すことができる.コード例を Listing 3.3 に示す.

始めはプログラミング言語として提案された Esterel であるが ,後になって回路設計言語としても用いられるようになった [31] . オープンソースで公開されている The Columbia Esterel Compiler は , CPU で実行可能な C 言語のプログラムに加え , Verilog のコードもしくは BLIF 形式の回路情報を合成することができる [32] .

**JHDL** (1998) JHDL[33] は, Java 言語をベースとした再構成可能システム向けの HDL である. オブジェクト指向言語の抽象化機構を利用することが可能となり, コードの再利用性を高め

```

public class mod4count2 extends Logic {

public static CellInterface[] cell_interface = {

3

in ("reset", 1),

in("mod4", 1),

4

out( "total_count", "wid" ),

param( "wid", INTEGER )

5

8

public mod4count2(Node parent, int length, Wire reset,

Wire mod4, Wire total_count) {

10

super(parent);

11

12

int i:

13

int width = total_count.getWidth();

14

15

bind("wid", width);

16

connect("reset", reset);

17

connect("mod4", mod4);

18

connect("total_count", total_count);

19

20

Wire addem = or(mod4, reset);

21

22

// Count up if addem is asserted. count down otherwise.

new upDownCounter(this, reset, constant(width,length),

23

addem, vcc(), total_count);

24

25

26 }

```

ることができるようになる. Listing 3.4 に示したコード例のように, Verilog や VHDL のようにモジュール間の接続などを全て記述する RTL 設計に近い. JHDL は PRSocket と呼ばれるコンポーネント間のインタフェースを提供しており,このインタフェースを用いることで FPGA の部分再構成 (partial reconfiguration) 機能が利用できるようになる.

Verischemelog (1999) Verischemelog [34] は, Scheme ベースのカスタムデジタル回路設計 ツールである. JHDL と同様のツールで, Verilog を抽象的に扱いマクロ言語を通して回路記述を 生成することでコードの再利用性と生産性を高めることを目標としている. Scheme がインタラクティブに実行可能な点に注目し,インタラクティブ実行中にも都度エラーや警告を行い設計の不備を発見できるように設計されている.

SystemVerilog (2002) SystemVerilog[35], [36] は, Verilog では抽象的な記述が困難だったため,新たなデータ型やオブジェクト指向,アサーションなどを導入し記述の抽象度を高めた HDL である.

しかしながらこれらの新機能が回路へ合成可能か否かは合成系の実装次第であり,整数型や共 用型など一部の機能を除いて多くの機能が合成できない可能性が高く,システム検証機能の強化 にとどまる改善となった.

ForSyDe (2002) ForSyDe (formal system design) [37] は,関数型プログラミング言語の考え方をハードウェア設計に応用可能であるか検討したものである. Haslell ベースの回路設計フレームワークとして実装されることを想定している. [37] では,高階関数や多相型,遅延評価など関数型言語の特徴的な機能からデータフローモデルのハードウェア設計に変換する数理モデルを構築

し,ハードウェア設計の抽象化の方法を説明している.Mulvery やその他の関数型の記述を採用するツールがハードウェアを生成する手法を数理モデルとして厳密に検討した論文であるといえる.

Bluespec (2003) Bluespec [38] はSystemVerologベースの独自言語であるBluespec SystemVerilog (BSV) を用いる回路設計ツールである. SystemVerilog の機能に加え,パラメトリック多相な function の定義や関数引数を使うことができるため,抽象度を向上させ再利用性の高い回路記述を行うことができるようになった.また型推論による静的型付けを行う言語であるため,例えば適切なバス幅を自動的に決定するなど記述の手間を省くことができる.

$C\lambda aSH$  (2009)  $C\lambda aSH$  [39] は,Haskell 言語ベースの関数型ハードウェア記述言語である. $C\lambda aSH$  以前のツールでは,if やパターンマッチなどのプリミティブ関数を用いた処理は回路に変換することができず,プリミティブ以外の別の関数を用いる必要があった( case の代わりに multiplexer が用意されているなど)。 $C\lambda aSH$  は新たに専用のコンパイラを用意することで,Haskell のプリミティブ関数を回路記述に用いることができるようになった.したがって,多相型(パラメトリック多相,アドホック多相)[22],ユーザ定義の高階関数,パターンマッチなどの Haskell の特徴的な機能全てを記述に利用でき,このツールならではのアーキテクチャ探索手法なども提案されている [40].また,ステートの遷移を表現するフレームワークを用いることで,クロックレベルの記述を実現することができるようになった.パターンマッチ文を用いてデコーダを記述しているコード例を Listing 3.5 に示す.

Haskell 言語は純粋関数型言語であるため,次のようなシンプルなルールで網羅的に回路への変換を行うことができる.

- 全ての関数はコンポーネントに変換される

- 全ての関数の引数は入力として変換される

- 関数の返り値は出力として返還される

- 関数適用はコンポーネントのインスタンシエーションとして変換される

Chisel (2012) Chisel [23] は, Scala 言語ベースのハードウェア設計ツールである.

Chisel 以前から公開されていた JHDL, HML, Verischemelog はマクロによって HDL よりも高い生産性で設計が可能であるが,未端のコンポーネントは HDL で記述されることがあり, Java や scheme はハードウェアの型やセマンティクスとマッチしないため厄介な問題を導いていると指摘している.そこで,ハードウェア用のプリミティブ型(Byte 型や Bool, Float 型)を定義し,ハー

Listing 3.6: Calculation of  $log_2(N)$  using PyMTL's function-level [5]

```

# FL implementation for calculating log2(N)

@s.tick_fl

def fl_algorithm():

# put/get have blocking semantics

s.out.put( math.log( s.in.get(), 2 ) )

```

Listing 3.7: Calculation of  $log_2(N)$  using PyMTL's cycle-level

```

# CL implementation emulates

# a 3-cycle pipeline

3 s.pipe = Pipeline( latency = 3)

4 @s.tick_cl

def cl_algo_pipelined():

if s.out_q.enq_ready():

if s.pipe.can_pop():

7

s.out_q.push( s.pipe.do_pop() )

8

9

10

s.pipe.advance()

11

if not s.in_q.deq_ready():

12

s.pipe.do_push( math.log( s.in_q.deq(), 2 ) )

```

ドウェアモジュールを定義するためのベースクラス (Bundle や Component) を用いたプログラミングフレームワークを提供することで、HDL と GPL の間の型システムとセマンティクスのギャップに由来する問題を解決した.また、Verilog HDL の代わりに C++のコードを生成し、Verilogシミュレータで実装するよりも高速なシミュレーションを実現できる.Listing 3.1 に示したコード例のように HDL に近い低い抽象度の記述が可能であり、末端のコンポーネントの記述も全てScala 言語のみで記述することができる.

著者らは , Chisel と Verilog HDL を用いて実装された 3-stages RISC-V を用いて Chisel の有効性を比較した . コード量は Verilog による記述の 1/3 となり , 動作速度や回路面積はほとんど変化しなかった . また , シミュレーション時間は Verilog シミュレータを用いた場合よりも 7 倍高速となった .

著名な RISC-V のオープンソースソフトコア実装のひとつとして知られる,カリフォルニア大 学バークレー校による RISC-V の実装にも利用されている [41], [42].

$\mathbf{PyMTL}$  (2014) PyMTL[5], [43] は ,Python ベースのカスタム回路設計ツールである.Function Level (FL), Clock Level (CL), Resister Transfer Level (RTL) の三段階の抽象度でハードウェアを設計でき,システムレベル設計ツールの一種であるとも言える.System Verilog のコードを Import する機能も提供しており,シミュレーションを行うこともできる.コード例を Listing 3.6 に示した.FL 記述は HLS に近いが,PyMTL においてハードウェア化される全てのオペレーションは変数 s に対する操作であり,HLS ではなく DSL によるシステムレベル設計である.

PyMTL は Mulvery と近い思想を持つツールであるため,次節で詳しく比較検討する.

#### 3.3.2 HLS ツール

Warp Processor Warp Processing [44] は,マイクロプロセッサ用にコンパイルされたバイナリを解析し,FPGA 用の回路を合成するツールである.バイナリを解析するため,コンパイル可

Listing 3.8: Calculation of  $log_2(N)$  using PyMTL's register-transfer-level

```

\begin{array}{lll} 1 & \# \ Part \ of \ RTL \ implementation \\ 2 & s.N = Reg(\ Bits32\ ) \\ 3 & s.res = RegEn(\ Bits32\ ) \\ 4 & s.connect(\ s.res.out,\ s.out.msg\ ) \\ 5 & \dots \\ 6 & @s.combinational \\ 7 & def \ rtl\_combN(): \\ 8 & s.res.in\_ = s.res.out + 1 \\ 9 & s.N.in\_ = s.N.out >> 1 \\ 10 & if \ s.N.out == 0: \\ 11 & s.res.en = Bits1(\ 0\ ) \\ 12 & else: \\ 13 & s.res.en = Bits1(\ 1\ ) \\ \end{array}

```

能なプログラミング言語であればふるまい記述に利用することができ,これは他のツールと大きく異なる特徴であるといえる.

Warp Processor は一度マイクロプロセッサ上でプログラムを実行し,プロファイラによって FPGA へオフロードする部分を動的に検出する.オフロードされる部分は一度デコンパイルされ,改めて回路に合成される.回路が FPGA に書き込まれたらプログラムの対応する部分を FPGA に計算を要求するように書き換える.これらの処理は全てプログラムの実行中,動的に行われる. Warp Processor は常にプロファイルを続け,最速に実行できるようにアーキテクチャを調整し続ける.例えば FPGA によって高速化が実現できないプログラムは,最終的に FPGA にオフロードされる部分が無くなり,マイクロプロセッサ上でのみ処理される.

LegUp LegUp [45] は, C 言語ベースのハードウェア/ソフトウェアの協調設計環境である.プログラムを高位合成する際, ハードウェアに適した部分とソフトウェアに適した部分があるため,プログラム全体をハードウェア化するとパフォーマンスが悪化することがある.このため,ハードウェア化に適切な部分のみをカスタム回路に変換し,その他の部分は MIPS ベースのソフトプロセッサ1上で実行するカスタム回路を生成する.

プログラムを MIPS プロセッサで実行しプロファイリングすることで,自動的にハードウェアとソフトウェアに分割する.中間表現として,様々なプログラミング言語のバックエンドで用いられている LLVM IR [46], [47] を用いている特徴がある.様々な言語をフロントエンドとして用いることができる可能性に加え,LLVM IR はハードウェアにおけるオペレーションとよく対応している特徴があるため,高位合成のための中間言語として十分な性能を発揮できるとしている.

浮動小数点演算への対応 [48] や複数のクロックドメインへの対応 [49] など, 2019 年現在も活発に開発が続けられているツールの一つである.

${f Darkroom}$  (2014)  ${f Darkroom}[50]$  は,画像処理のための  ${f DSL}$  とコンパイラを提供する.画像処理では  ${f DRAM}$  へのアクセス帯域を大きく消費するため,ラインバッファを用いアクセス帯域を小さく保つようにコンパイルが行われる. ${f Darkroom}$   ${f DSL}$  はデータフロー型のプログラミングモデルを用いるため,容易に有効非巡回グラフ (directed acyclic graph;  ${f DAG}$ ) を生成できる. ${f Darkroom}$  コンパイラは画像処理の記述から生成された  ${f DAG}$  をシリアライズし, ${f ASIC}$  や  ${f FPGA}$  のための  ${f RTL}$  記述を生成する.

$<sup>^1\</sup>mathrm{HDL}$  などで記述された合成可能 (synthesizable) なプロセッサ . FPGA 上で動くプロセッサなどとして利用される .

Darkroom 以前から,C++のマクロを用いて実装された画像処理 DSL の Halide [51] が利用されている.Halide を用いた HDL ツールとして,アカデミックでは [52],商用では日本の Fixstars 社による実装 [53] などが公開されている.Halide は CPU や GPU 向けに設計された DSL であるため,ウィンドウサイズや画像サイズを抽象的に定義できる.このような特徴を持つ場合,実行時までデータサイズが確定できない問題があるため, $Darkroom\ DSL$  は画像やフィルタのウィンドウサイズなどが静的で固定なものとなるように定義されている.

Intel HLS, Vivado HLS 現在最も広く使われているといえる HLS ツールとして,FPGA 大手ベンダである Intel 社の Intel HLS [54] および Xilinx 社のの Vivado HLS [55] が挙げられる.両ツール共に C/C++をベースとした HLS ツールで,プリプロセッサ命令(pragma)を用いて合成される回路のアーキテクチャを制御する.例えば Vivado HLS では,ループを展開し 1 ステートで計算するための命令(unroll)や,FPGA 上のメモリを複数利用することでメモリアクセスの帯域を増やすための命令(array\_partition)などの命令が用意されている.C/C++の言語仕様では並列実行が考慮されていないため,ユーザはデータアクセスパターンの制御などを自身で管理する必要があり,並行プログラミング技法が必須の知識となっている.

#### 3.3.3 システムレベル設計ツール

Ruby (1990) 1990年に,Ruby という名の回路設計フレームワークが提案されている [56].これは Mulvery が利用する Ruby[57] とは異なるものである.Ruby は 2 つの回路の関係性の表現方法を定義したもので,例えば R,S という回路があったとき R;S は R から S にコネクションのある関係を表す.他の関係性の表現を組み合わせて数理論理学的に回路の正当性を検証を行うための技法をまとめたフレームワークである.シストリックアレイ [58] のような,多数の小さな計算要素の並ぶアーキテクチャの設計と検証などに利用されている [59].

**HML** (1995) HML [60], [61] は,ML 言語ベースのハードウェアモデリング言語である.ML 言語の高度な型システムを用いて型安全なプログラミングモデルを提供する.型推論を持つ言語であるため,ユーザは型を明示せずともインタフェースの接続を安全に行うことができる.ふるまい記述を行うこともできるが複雑な記述は困難である.モジュール間の接続を得意としているため,システムレベルの設計ツールとして分類した.2019 年現在,ツールは公開されておらず,利用することができない.

MATLAB/SimuLink の HDL Coder HDL Coder [62], [63] は MATLAB/SimuLink [29], [30] のプログラムを元にカスタム回路を生成するツールである.信号処理や制御システムの分野では MATLAB/SimuLink がしばしば利用されている.これらのモデリングはデータフロー型のパラダイムで行われるため,回路を合成するツールとしても利用されている.特に SimuLink は様々な要素ブロックを組み合わせたブロック図を作成し,VLSI や DSP システムなどのシミュレーションを行うシステムレベル設計ツールであったため,FPGA 向けの回路の生成も自然な機能である.したがってハードウェアエンジニアが利用するため設計されたツールであり,ソフトウェアエンジニアが利用するためのものではない.

${f CAOS}$  CAOS (CAD as an Adaptive OpenPlatform Services)[64] は, FPGA アクセラレーションを用いた HPC システム向け開発ツール (ワークフロー) である.これまでに説明したツールと大きく異なり,マルチノードかつ,各ノードに複数の FPGA が搭載されていることを想定したシ

Listing 3.9: Example of kernel description using MaxCompiler

```

1 HWType flt = hwFloat(8,24);

2 HWVar x = io.input("x", flt);

4 HWVar x prev = stream.offset(x, - 1);

5 HWVar x next = stream.offset(x, +1);

HWVar\ cnt = control.

7

count.simpleCounter(32, N);

HWVar sel nl = cnt > 0;

Q

10 HWVar sel nh = cnt < (-N1);

11

HWVar sel m = sel nl \& sel nh;

12

13 HWVar prev = sel nl ? x prev : 0;

14 HWVar next = sel nh ? x next : 0;

15 HWVar divisor = sel m ? 3.0 : 2.0;

16

17 HWVar y = (prev + x + next)/divisor;

18 io.output("y", y, flt );

```

Listing 3.10: Example of Manager on MaxCompiler [6]

ステムをターゲットとしている.ノード間の接続を記述したシステムテンプレート,各ノードの持つ計算資源を記述したノードテンプレート,FPGA にデプロイされる計算カーネルを記述したアーキテクチャテンプレートの 3 種類の記述によって複雑な HPC システムの構成を記述する.アプリケーションは C/C++や OpenCL を用いて記述し,API を通して FPGA にデプロイされる計算カーネルを呼び出すことができる.CAOS のコンパイラはテンプレート・アプリケーションコード・計算カーネルを元にシステム全体のプロファイリングを行い,最適なスケジューリングとマルチノード環境へのマッピングを自動的に行う.ただし,計算カーネル自体は HDL で記述されている必要があるため,事前に他のツールを用いて設計しておく必要がある.

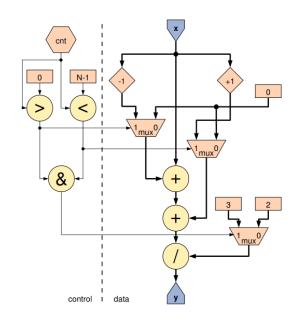

${f MaxCompiler}$  Maxeler 社の開発する商用ツールである  ${f MaxCompiler}[6]$  はカスタム回路設計ツールである。命令シークエンスを記述する Kernel , カーネルと  ${f I/O}$  を組み合わせ統合する Manager , FPGA 上のハードウェアを制御するソフトウェアの Host Application の  ${f 3}$  層に分けてシステムを記述する。Kernel と Host Application は  ${f MaxCompiler}$  用に作られた Java 言語ベースの  ${f DSL}$ :  ${f MaxJ}$  を用いて記述され,Host Application は  ${f C/C}$ ++や Fortrun によって記述される.

Kernel の記述の例と生成されるハードウェアを表現したグラフを Listing 3.9 および図 3.2 に示した.また,Manager の記述の例を Listing 3.10 に示した.Kernel の設計の粒度は非常に細かく,この部分は RTL 設計に近いといえる(ただしクロックとの同期を記述しないため,RTL 設計とは異なる).

■ 3.2: The graph of the synthesized hardware [6]

# 3.4 本研究の位置付け

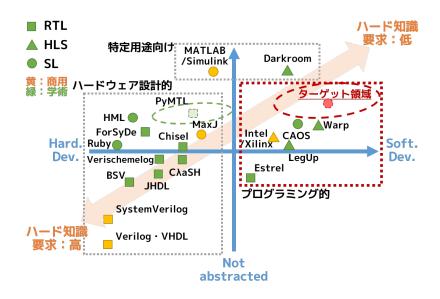

図 3.3 に,先行研究・ツールと比較した本研究の位置付けを示す.記述の指向を「ハードウェア設計的」「プログラミング的」「特定用途向け」の三種類に分類した.ハードウェア設計的なツールは  $\mathrm{HDL}$  の改善を念頭においたツールであり, $\mathrm{DSL}$  のツールがほとんどである.プログラミング的なツールは  $\mathrm{HLS}$  ツールを指しており, $\mathrm{C}$  や  $\mathrm{Java}$  などのプログラミング言語を使って,動作記述を行うものである.特定用途向けのツールはある一定の領域に絞り込んだツールを指し,専用の  $\mathrm{GUI}$  ツールやフレームワークによって簡易に動作を記述することができるツールである.

これまでの多くの研究やツールは、ソフトウェア開発を行うプログラマ向けのツールではなく、ハードウェア設計者の負担を軽減するためのハードウェア設計者のためのツールとして開発されている.特定用途向けに事前にチューニングを施されたツールを除けば、プログラミング的なツールに分類されたツールであっても、ユーザによってコードや生成物のチューニングが施されることが前提となっている.したがってハードウェアの知識の少ないユーザが実用的な回路を設計するためには、非ノイマン型計算機アーキテクチャへの理解やツール毎の最適化戦略への理解など、プログラミング以外の部分への多大な学習コストを要する.

本研究では,プログラミング的かつ非特定用途向け(つまり様々な領域に適用可能)であるツールでありながらも,ハードウェアの知識に基づくプログラムの設計や生成物の最適化を最低限に低減することを目標とする.本研究は,現在広く用いられている GPGPU のように,FPGA が一般的に広く利用される汎用アクセラレータとして活用されるための重要な技術研究となることを目指す.

☑ 3.3: Comparison of tools

## 第4章 フレームワークを用いたアーキテクチャレ ベルの最適化

# 4.1 複数のツールを組み合わせた ${ m IoT/CPS}$ エッジデバイス向けフレームワーク

IoT(Internet of Things) が注目を浴び,センサと通信機能を持つ様々なデバイスが開発されている.このようなデバイスでは,センサ入力やデータの出力のための機能を備えた LSI チップも数多く製品化されており,センサデータの種類や量の増加,分解能の向上などに伴いより高度なアルゴリズムを用いたデータ加工によるアプリケーションの実現が期待される.しかしながら,データ入力やデータ加工の処理コストの問題が生じてくる.

一方,目的とする処理をハードウェア回路として並列に実行する FPGA を用いたアクセラレー タが,処理能力や電力効率の面で注目されている.スマート家電や自動運転など様々な分野で高い 分解能のセンサを多数搭載するシステムが登場し,今後も増加していくことが予想される.この ようなシステムにおいて FPGA を利用することは,大まかに分けて2種類の利点がある.ひとつ は,プロトタイピングのために FPGA を活用するものである.回路を繰り返しアップデート可能 な FPGA を用いてコンセプトの実証などを行い , 十分大量に生産することが期待できる最終的な 製品では ASIC 化するなどしてコストや電力性能を改善する開発プロセスとなる.もう一方は , 最 終的な製品にも FPGA を利用する場合である.カメラやテレビにおける画像処理のように,処理 の高速性が求められかつ顧客毎や技術の変化に応じて処理内容が変化しうるような場合に FPGA を搭載し様々な状況に対応できるように設計されたデバイスが存在する.またネットワーク機器 の分野では物理層をセンサとアクチュエータのように捉えることができ,ファームウェア更新を するようにパケット処理回路を更新することが可能となる.しかしながら,一般に FPGA による アクセラレータの設計は Verilog HDL や VHDL といったハードウェア記述言語を用いてレジスタ 転送レベルで行うため,ソフトウェアベースのシステムと比べて開発のコストが大きくなり,ま た高級言語によって記述された既存のソフトウェアを RTL 記述に変換する場合も多大なコストを 要する.

近年では,C 言語をベースとした Vivado HLS が無償で利用でき,さらに JavaRock[65] や JavaRock-Thrash[66][67],Synthesijer[68] といった Java 言語をベースとした高位合成ツールが 開発されている.これらのツールの登場によって,FPGA 回路設計のコストの低減と,これまでのソフトウェア資産の再利用が期待される.しかしながら,センサインタフェースや DRAM といった外部モジュールとの通信ではタイミングが重視され,クロックを意識しない高位合成ではタイミング調整が困難であるという問題があった.

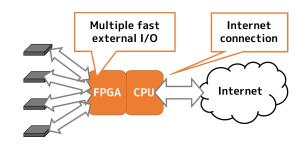

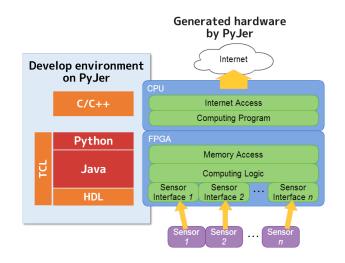

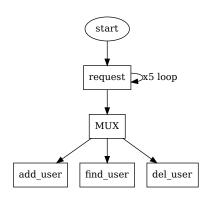

この章では,複数の高速なデータ入力とインターネットへのデータ出力が必要となる組み込みシステムのプロトタイピングのためのフレームワーク PyJer をの研究について説明する.複数の高位合成ツールと RTL 設計を組み合わせることでソフトウェアベースの開発に近いシステム開発の実現を目指した.

なお,本章で説明する PyJer は Github にて公開されている [69].

## 4.1.1 関連研究

## 高位合成ツールにおける問題点

高位合成ツールを用い、FPGAによるアクセラレータを実装する研究が数多く存在する.その中で,Vivado HLS を用いて開発した行列積アクセラレータと PyCoRAM および HDL で開発した行列積アクセラレータの性能比較がある [70].ここでは,行列積での計算よりも FPGA-CPU間の I/O にかかる比重が大きく,Vivado HLS のみによるアクセラレータよりも NEON 命令を用いて CPU 上のみで行う処理のほうが高速であると報告している.PyCoRAM はメモリアクセスチューニングに特化したツールであるために,計算カーネルの設計は HDL で行う必要があった.PyCoRAM および HDL を用いた開発では,PyCoRAM によってメモリチューニングは達成できるが,PyCoRAM で用いる計算カーネルの HDL による記述について,抽象度の低さに起因する開発の敷居の高さが指摘されている.

#### センサ入力を必要とするシステムの構築

これまでに、マイコンとセンサを用いたシステムを FPGA 上に移植する研究が行われている. [71] では、マイクロコントローラ上に実装された倒立振子制御のシステムを Java 言語ベース高位合成ツール JavaRock を用いて FPGA 上に専用ハードウェアとして移植を行い、その性能評価を行った.ここでは、センサデータの取得に多くの時間が必要であることが指摘され、センサ値取得とセンサデータの処理が同時に実行できる FPGA によって高速化が可能であると報告している.本研究では IoT に向けたデバイスを意識し、システム全体の FPGA 移植ではなく、容易なインターネットアクセスの実現のため CPU との連携も考慮する.

また, Electronic System Level(ESL) synthesis を用いた高速で低消費なワイヤレスセンサシステムの実装を行っている研究もある [72]. ASIC での実装の前にモデルベースの記述と FPGA によってプロトタイピングとチューニングを行うことで短期間の開発と高い性能の実現が両立できたことを報告している.

## 4.1.2 PyJer の概要

PyJer は , センサ入力が必要となる組み込みシステムの高速なプロトタイピングを行うための開発フレームワークである . この章ではその具体的特徴について説明する .

## 目的

センサ入力が必要となる組み込みシステムにおいて,センサの出力が高速であったり入力するセンサが多い場合,一般的な汎用マイクロコントローラではセンサのハンドリングが困難になると考えられる.このため,センサ入力はデータ処理とは並列に行えるシステムが構築できる必要がある.PyJer ではこれを FPGA にオフロードし,大量のデータの処理が必要なシステムのプロトタイピングを効率よく行える環境を実現する.また,サーバなどの外部システムとの通信については,TCP/IP などこれまでのソフトウェア資源を用いた開発が有効であると考えられる.

これらのことから, PyJer の基本的方針として, FPGA ではセンサ入力やデータ処理の一部を, CPU では通信や複雑な処理など既存のソフトウェア資源が活きる部分を受け持つものとした.

☑ 4.1: Structure where data flow is difficult to be modified

## 特徴

## インターネットアクセスと SoC の活用:

${

m IoT}$  を意識したデバイスを開発する場合,デバイスのインターネットを通した通信が重要となる. ${

m FPGA}$  のみでシステムを構築する場合,インターネットへの接続の実現には大きなコストを要する.そこで  ${

m PyJer}$  は  ${

m SoC}$  をターゲットとし, ${

m OS}$  が動作する  ${

m CPU}$  と  ${

m FPGA}$  の連携を実現する.これによってインターネットを通した通信に関する多くのソフトウェア資源を用いることが可能となり,効率のよいプロトタイピングを行うことができる.

## フレキシビリティの高いアーキテクチャ:

データ出力機構を CPU を通したものでなく別の機構に変更する場合 ,設計次第では変更の影響の範囲が広くなりシステムの変更が複雑なものとなってしまう(図 4.1). そこで PyJer では CoRAM アーキテクチャを導入し , ユーザはその実装を意識することなく高いフレキシビリティを得ることができる . これはロジックの実装からデータフローの定義を分離して実装を行うことで実現される .

#### 抽象度の高い記述による設計:

高速なプロトタイピングのために、開発全体を通して抽象度の高い設計を行うことができる.これまでの Vivado HLS[55] のような汎用の高位合成ツールのみではハードウェアの詳細なチューニングが行いにくく,PyCoRAM[73] のような詳細なチューニングを支援するようなツールは HDLによる設計のチューニングを支援することを想定したものであった.PyJerでは,設計の段階に応じて複数のツールを使い分けることで,ツールごとの導入して得られるメリットそれぞれを活用することができる.またビルド全体の自動化によって,複数のツールの使用によって発生する開発の煩雑さを解消した.

#### 開発の手順

PyJer では,FPGA チップベンダの提供する回路合成・配置配線ツールを用いて行うべき作業も含めてビルド作業の多くを自動化した.これによってプロトタイピングがなるべく早い開発サイクルで行える開発環境を目指す.具体的には,以下の手順で開発を行う.

1. Verilog HDL を用いたセンサとのインタフェースの記述

表 4.1: Software-based development environment for mic data processing

| CPU      | ARM Cortex-A9 667MHz                 |  |  |

|----------|--------------------------------------|--|--|

| DRAM     | DDR3-1066, 533MHz, 32bit wide, 512MB |  |  |

| OS       | Linux 4.0.0-gd94f3f3                 |  |  |

| 実装に用いた言語 | C (g++4.6.3)                         |  |  |

- 2. Java を用いデータの処理機構の記述

- 3. Java を用いたサブモジュール間の接続の定義

- 4. Python を用いたデータフローの定義

- 5. Vivado TCL を用いた外部との接続の定義

- 6. make コマンドによるビルド

## 4.1.3 PyJer の設計方針

PyJer ではセンサ入力処理を FPGA にオフロードし並列化し,効率化を図る.ここでは,センサ入力を必要とする組み込みシステムにおける重要事項を考察し,PyJer の設計方針について説明する.

## センサ入出力のハードウェアオフロード

予備実験として,センサ入力処理のソフトウェアのみによる実装と評価を行った.この予備実験においてはフレームワークのターゲットとしている  ${

m Zynq-7000}$  においてプログラマブルロジック  ${

m (PL)}$  部を使用せず,プロセッシングシステム  ${

m (PS)}$  部のみで実装を行う形式とした.ソフトウェア開発環境を表 4.1 に示す.予備実験では,シリコンディジタルマイク  ${

m SPM0405HD4H}$  を使用した.このマイクは  ${

m PDM}$  波形を出力し,本研究ではその出力周波数を  ${

m 2MHz}$  に設定した.

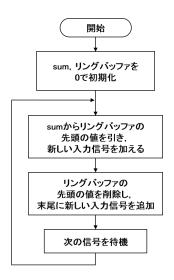

本研究において,PDM 波形をアナログ値に変換する手順は,信号を 512[bit] のリングバッファにバッファリングし,信号 1[bit] の到達ごとにその総和を求めるものとした.より具体的な処理の手順を図 4.2 に示す.この処理を C 言語で実装し,処理に要する時間を OS の提供する clock 関数を用いて計測した.ただし clock 関数の計測精度は 10[ms] のため,処理を  $10^9$  回繰り返しその平均値を処理に要する時間とした.また,センサ入力の代用として,変数の読み出しを行っている.

計測に使用したプログラムを図 4.3 に示す.このプログラムによって得られた結果は図 4.4 の通りとなった.処理 1 回あたりに要した時間は約  $0.0511[\mu s]$ ,すなわち 1 秒あたりの処理レートは  $19.6[\mathrm{MHz}]$  であった.同じマイクを複数接続することを考えた場合, 9 つまで接続が可能である.

## CoRAM アーキテクチャの導入

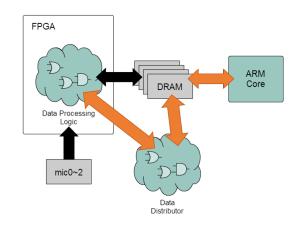

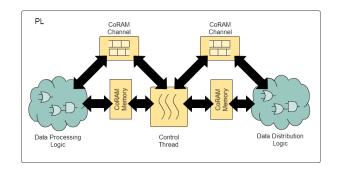

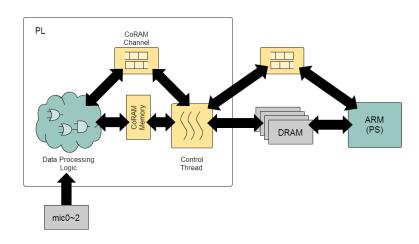

フレキシビリティの高いアーキテクチャを実現するため , PyJer の生成する IP コアは CoRAM アーキテクチャ [74] の形式をとる . CoRAM アーキテクチャの形式をとる場合 ,図 5.29 に示すように IP 内部の各モジュールはそれぞれ CoRAM と呼ばれる RAM および Control Thread と接続す

☑ 4.2: Flowchart of PDF signal DA conversion

```

#define BUFF_SIZE (512)

#define BIAS_LEVEL (256)

#define NUM_ITERATION (1000000000)

int main(void)

{

...

start = clock();

for(i = 0; i < NUM_ITERATION; i++){

buff_tail = (buff_tail + 1) % BUFF_SIZE;

sum = sum - buff[buff_tail] + input;

output = sum - BIAS_LEVEL;

buff[buff_tail] = input;

}

end = clock();

...

}</pre>

```

☑ 4.3: The program of time measurement of mic data processing

る FIFO を両方向に持つ.Control Thread と呼ばれるデータフローを制御するモジュールによって CoRAM 間のデータ転送が行われる.このアーキテクチャを用いることで,データフローの変更にロバストなシステムが構築できる [74].図 4.6 のようにデータ配信機構を SoC の CPU 部から FPGA 内のロジックに変更するような場合,Control Thread によるデータの転送先を変更するのみでよい.

## Vivado による合成・配置配線の自動化

開発サイクルを速めるため, Vivado TCL を用い合成・配置配線の自動化を実現する. Vivado TCL は, Xilinx 社が提供する統合開発環境 Vivado(Vivado IDE) をバッチ制御するために利用する言語である. Vivado TCL を用いてあらかじめメタにプロジェクトの設定を記述しておくことが可能である. これを用いて合成・配置配線の制御を行うのは煩雑なものであるため, プロトタイピングのために自動化ツールを書くのはコストが大きい. Vivado IDE の生成するプロジェクト

Processing time: 51050000[us]

Average processing time: 0.051050[us]

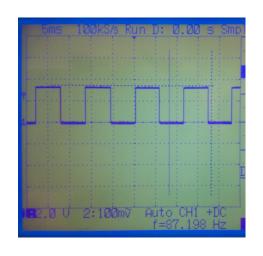

## ☑ 4.4: Measured processing time of mic data processing

☑ 4.5: Hardware architecture with CoRAM

フォルダを用いずに開発することで自動的に生成されるファイルの除外の手間が省け, Git などの バージョン管理システムによるプロジェクトの管理を容易に行うことができるメリットも得られるため, 構築したフレームワークにおいてこの機能を実現する.

## 4.1.4 PyJer が実現するシステムのアーキテクチャとデータフロー

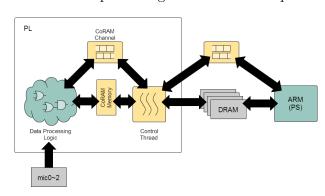

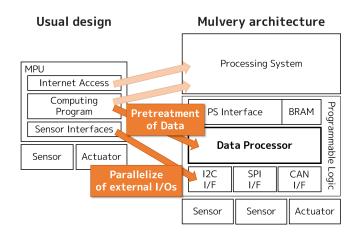

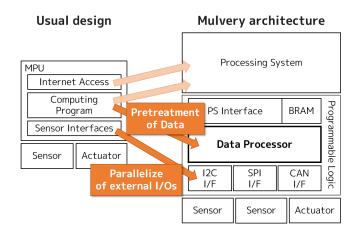

## アーキテクチャ

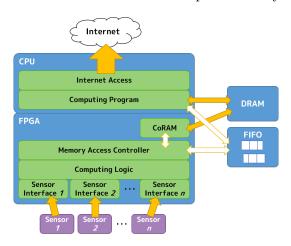

PyJer によって実現されるシステムのアーキテクチャを図 4.18 に示す.従来の設計では複数のセンサが 1 つの CPU に接続される形であった.対して PyJer を用いたシステムのアーキテクチャでは,センサ入力に必要な処理はハードウェアにオフロードされ,並列化される.また,データ処理機構の一部もハードウェアにオフロードすることができる.この章では,PyJer の生成するアーキテクチャに含まれる重要なコンポーネントについて説明する.

## Sensor Interfaces

センサとの通信と , センサデータのデコード , センサへの命令のエンコードなどを受け持つ . クロックレベルのタイミング制御が必要なため ,  $\operatorname{Verilog\ HDL}$  で記述されることを想定している .

## Computing Logic

各センサから収集したデータの処理を行う.また, Memory Access Controller に指示を送り, CPU-FPGA 間のデータ転送のタイミングの制御なども行う. Java 言語によって記述され, Synthesijer を用いて高位合成される.

#### Memory Access Controller

FPGA 内の CoRAM と DRAM の間のデータ転送を行う, Control Thread のこと. Python 言語によって転送タイミングの設定などを行ない, PyCoRAM によって生成される.

#### Computing Program

$\mathrm{DRAM}$  を通して  $\mathrm{PL}$  部からセンサデータを受け取り,ソフトウェア的に行ないたいデータ処理や,外部システムに出力する前のデータ整形などを行う. $\mathrm{C/C}++$ 言語で記述されることを想定している.

☑ 4.6: Arcitecture when data distribution is performed by a module in PL

☑ 4.7: System architectrue that PyJer generates

#### Internet Access

外部システムとの通信を受け持つ、既存のソフトウェア資源を用いた Ethernet や Bluetooth 等による外部システムとの接続を想定している。

## データフロー

4.1.4 にて説明したアーキテクチャ内でのデータの流れについて説明する.

## センサデータの取り込み

各 Senser Interface はそれぞれ独立してセンサとの通信を行ない,センサデータの取り込みを行う.例えば PDM 信号であれば, Sensor Interface はバッファリングやフィルタリングを行ない, Computing Logic からの要求に応じて即座にデコード済みの最新のセンサデータを出力することができる.

## FPGA から CPU へのデータの受け渡し

Computing Logic は,処理が完了したデータを CoRAM へ蓄積する. Computing Logic は任意のタイミングにて, Memory Access Controller に対して CoRAM のデータを, CPU が自由にアクセスできる DRAM の領域へと転送させる命令を送る.

## CPU-FPGA 間の同期

CPU-FPGA 間には , PyCoRAM による Memory Access Controller を通した FIFO が用意され

☑ 4.8: Tool hierarchy

☑ 4.9: Example description of data processing mechanism using Synthesijer

ている.このため  $Computing\ Logic\$ は  $CPU\$ との簡単なデータのやりとりや,同期的に CoRAM のデータの転送を行うことができる.

## 4.1.5 PyJer の使用法とその実装

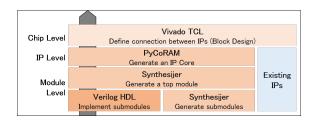

この章では, PyJer の使い方とその実装について述べる. 使用したツールの階層構造を示す図を図4.8 に示し, 最下層から詳細を説明していく.

## PyJer を用いたシステム設計の手順

## データ入力機構,データ処理機構の設計:

データ入力機構およびデータ処理機構について、それぞれサブモジュール単位で設計を行う.また、サブモジュールの接続の定義を行い、トップモジュールを作成する.この段階でデータの入力・処理・CoRAMへの出力までの記述を行う.

設計には基本的に Java 言語を使用し(図 4.9), Java 言語ベース高位合成ツールである Synthesijer によって Verilog HDL へとコンパイルが行われる. センサとの通信などクロックサイクルレベル の設計が必要な部分に関しては Verilog HDL を直接用い設計を行う(図 4.10). 実装・生成された サブモジュール群は Synthesijer の機能を用いてひとつのモジュールとして結合される(図 4.11).

Java コードからのセンサデータへのアクセスのサンプルコードを図 4.1 に示す. Sensor Interface と Computing Logic の接続の定義は ,Synthesijer の利用方法に従い Top モジュールと呼ばれるコード内で行う. 正しく接続の定義を行えば ,Computing Logic 側ではクラス変数がクラス外部から書き換えられるような形でセンサデータが入力される. すなわち ,Top モジュールにて接続先に設定した変数にアクセスすることでセンサデータを得ることができる. Top モジュールの Computing Logic の I/O の定義にて , <name>\_in, <name>\_we というポートを用意し we を常に HIGH にすることで , in に書き込んだ値を Computing Logic の Java コード内のクラス変数 <name>に反映させることができる.

Listing 4.1: Sensor data acquisition in Synthesijer program

```

// ---モジュール Top-

public class SampleTop {

2

public static void main(String... args){

3

4

// Computing の LogicI/の定義 O

5

HDLPort core_sensor_data_0_in = sampleCore.newPort( \

6

"i_sensor0_data_in", HDLPort.DIR.IN, \

7

HDLPrimitiveType.genVectorType(32));

8

HDLPort core_sensor_data_0_we = sampleCore.newPort( \

"i_sensor0_data_we", HDLPort.DIR.IN, \

10

HDLPrimitiveType.genBitType());

11

12

13

^{\prime}/ センサインタフェースの ^{\it I/}の定義 ^{\it O}

14

\dot{H}DLModule sensorInterface = \

15

new HDLModule("sensor_interface_sample", "clk", "rst");

16

HDLPort sensor_data = sensorInterface.newPort("data", \

17

HDLPort.DIR.OUT, HDLPrimitiveType.genVectorType(32));

18

19

20

/ センサインタフェースののインスタンス生成

21

\acute{\text{HDLInstance}} instanceSensorInterface0 = \setminus

22

sampleTop.newModuleInstance(sensorInterface, \

23

"sensorInterface0");

24

HDLInstance instance Sensor Interface 1 = \

25

sampleTop.newModuleInstance(sensorInterface, \

26

"sensorInterface1");

27

28

29

// 接続の定義

instanceSample.getSignalForPort(\

30

31

32

instanceSensorInterface0.

getSignalForPort(sensor_data.getName()));

33

instanceSample.getSignalForPort(\

34

sample_sensor_data_0_we.getName()).setAssign(null, \

35

HDLPreDefinedConstant.HIGH);

36

37

38

39

40

//---Computing\ Logic---

41

42

public void sampling_mic_data(){

43

while (true){

44

for (int i = 0; i < BUFSIZE\_MIC\_DATA; i++){

45

buffer_sensor0_data[i] = i_sensor0_data;

46

buffer_sensor1_data[i] = i_sensor1_data;

47

wait_sampling_period();

48

49

50

}

51

```

## Listing 4.2: Example of data transfer to DRAM

```

1 private void send_data_to_dram()

// データを転送する

2

for (int i = 0; i < 4096; i++){

3

4

o_mem_addr = i;

o_mem_d = result_data[i];

5

6

o_mem_we = true;

for (int j = 0; j < 1; j++);

7

o_mem_we = false;

8

}

9

10

// Memory Access Controller ヘトリガ送信

11

o_{comm_d} = 0; // unused value

12

o_{\text{comm-enq}} = \text{true};

13

for (int j = 0; j < 1; j++);

14

o\_comm\_enq = false;

15

16

17

for (int j = 0; j < 10; j++);

18

// 受信完了通知を待つ

19

while (i_comm_empty);

20

while (!i_comm_empty){

21

22

o\_comm\_deq = true;

for (int j = 0; j < 1; j++);

23

24

o_{\text{comm\_deq}} = \text{false};

25

}

26

```

## Listing 4.3: Example of Memory Access Controller

```

iochannel = CoramIoChannel(idx=0, datawidth=32) # ARM side

ram = CoramMemory(idx=0, datawidth=DSIZE * 8,

size=RAMSIZE, length=1, scattergather=False)

channel = CoramChannel(idx=0, datawidth=32) \# FPGA \ side

def body():

6

unused_req_1 = channel.read()

8

\# Translate dataset from BlockRAM to DRAM

9

ram.read_nonblocking(DAT_SRC+(0*SPSIZE), \

10

DAT_DST+(0*ADDR_WIDTH), SPSIZE)

11

ram.read_nonblocking(DAT_SRC+(1*SPSIZE), \

12

DAT_DST+(1*ADDR_WIDTH), SPSIZE)

13

ram.wait()

14

15

channel.write(1)

16

17

while True:

18

body()

19

```

```

module SensorInterface

(

input clk,

input rst,

...

);

...

always @(posedge clk) begin

// データ入力の処理

```

☑ 4.10: Example description of sensor data processing using Verilog HDL

```

@synthesijerhdl

public class DataProcessorTop{

public static void main(String... args)

HDLModule dataProcessorTop \\

= new HDLModule("HataProcessorTop", "clk", "reset");

// 上位層への I/F の定義

HDLModule dataProcessor \\

= new HDLModule("DataProcessor", "clk", "reset");

// DataProcessor の I/F の定義

HDLModule sensorInterface \\

= new HDLModule("SensorInterface", "clk", "reset");

// SensorInterface の I/F の定義

/*** インスタンスの生成 ***/

HDLInstance instanceDataProcessor \\

= dataProcessorTop.newModuleInstance(dataProcess...

/*** I/O の接続の定義 ***/

instanceDataProcessor.getSignalForPort("clk").set...

```

■ 4.11: Example of Top module using Synthesijer

データ処理機構から DRAM ヘデータを転送するためのサンプルコードを図 4.2 および図 4.3 に示す.メソッド send\_data\_to\_bram が呼び出されると,クラス変数 result\_data の内容を CoRAM に転送し,その後トリガを受け取った Memory Access Controller が CoRAM メモリの内容を DRAM に転送する.

## データフローの定義:

この段階では, Python 言語によって, データフローの定義 ( Memory Access Controller の定義 ) を行う.

CoRAM アーキテクチャ実装のためのフレームワークとして, Python 言語ベースのツールである PyCoRAM を用いた. これによって Synthesijer によって生成されたトップモジュールを含めた IP が生成される.

## VivadoTCL による IP の接続 ( Block Design ) の定義:

最後の段階として,Block Design を行うための Vivado TCL の記述を行う.PyJer はこの TCL スクリプトのテンプレートを提供し,ユーザは外部ピンへの出力や PyCoRAM が生成した IP への入出力の変更などその一部の修正を行うのみでよい.

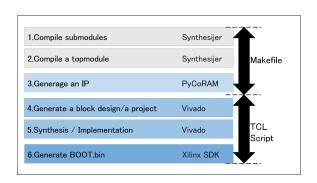

#### make コマンドによるビルドの実行:

ここまでの記述が完了したのち, make コマンドのみで全てのツールを通した回路の合成・配置 配線が行うことができる.

- 1 update\_ip\_catalog -rebuild -scan\_changes

- 2 report\_ip\_status —name ip\_status

- 3 upgrade\_ip -vlnv <IP Name> [get\_ips <Component Name>]

■ 4.12: Build flow and tools used for build automation

## Vivado IDE における合成・配置配線の全自動化

Vivado IDE の生成するプロジェクトフォルダを用いる場合, 1) ソースコードやファイルの管理がしにくい, 2) Vivado IDE でバッチ処理を行う場合に IP の更新時に Block Design でエラーが起こりやすい, という問題があった. そこで PyJer では Block Design を生成するための TCL スクリプトを用意するという方法によって解決した.

なお、Vivado IDE の GUI によって構築した Block Design は、Vivado IDE の File Export Export Block Design から TCL コードとしてエクスポートが可能であるが、これを利用した合成は困難であった.これを用いてバッチ処理によるビルドを行うとき、外部から IP が更新された際に図 4.4 の手順で IP の更新を行うとビルドが停止してしまう問題に直面したためである.図 4.4 のスクリプトは GUI で Upgrade Selected IP を行う際に実行されるものである.

#### Makefile および Vivado TCL によるビルド全体の自動化

PyJer のユーザは , SD カードブートを行うための BOOT.bin ファイルを  $\max$  コマンドのみによって自動的に生成することができる .

BOOT.bin を生成するために必要な手順を図 4.12 に示す.複数のツールを取り入れたことによってビルドの手順が複雑なものとなっている.このため,ビルド全体を自動的に実行するための Makefile を作成し,Vivado IDE による合成・配置配線・BOOT.bin の自動生成のための TCL スクリプトを記述した.ツールのプログラムの改変を伴う複数ツールの統合は困難であり拡張性にも欠けることから,各ツールに Verilog HDL ファイルを生成させ,最終的にそれらを 1 つの IP に組み立てるという方針でビルドツールを実装した.

表 4.2: Platform used for experiment and verification

| 評価ボード                | Digilent ZedBoard                        |  |  |

|----------------------|------------------------------------------|--|--|

| $\operatorname{SoC}$ | Xilinx Zynq-7000 AP SoC XC7Z020-CLG484-1 |  |  |

| DRAM                 | DDR3-1066, 533MHz, 32bit wide, 1GB       |  |  |

| OS                   | Linux 4.0.0-gd94f3f3                     |  |  |

| mic                  | SPM0405HD4H 2MHz PDM                     |  |  |

■ 4.13: Position of sound source and its signal

## 4.1.6 評価方法

## 実験・評価に用いるプラットフォーム

フレームワークは Xilinx 社の SoC である Zynq-7000 を使用することを想定して構築した.このため,フレームワーク構築に必要な実験や評価を行う環境として,Zynq-7000 を搭載した Digilent 社の評価ボードである ZedBoard を使用した.

構築したフレームワークはマイクロコントローラのみではセンサ入力の処理が困難なシステムをターゲットとしている.したがって量の多いデータ入力を行うために,4.1.6 節で述べる評価用アプリケーションで用いるためのセンサとして 2MHz で PDM 出力を行うマイクを選択した.

## 構築したフレームワークを用いて実装するアプリケーション

評価のために,構築したフレームワークを用いて次のようなアプリケーションを実装するものとした.

## 音源位置推定システム:

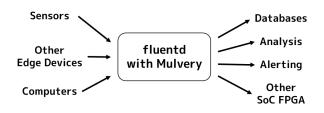

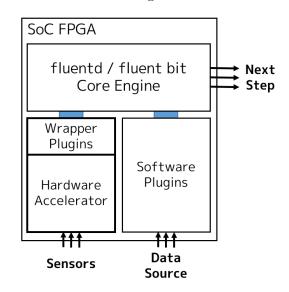

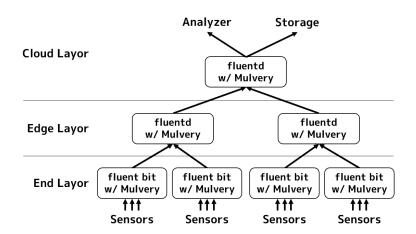

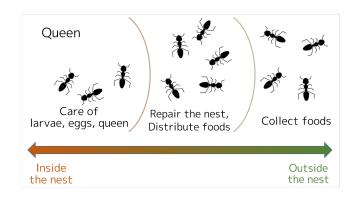

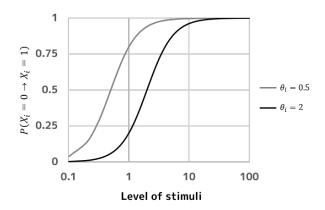

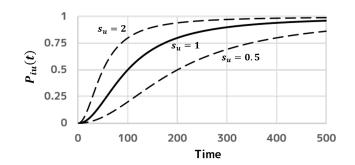

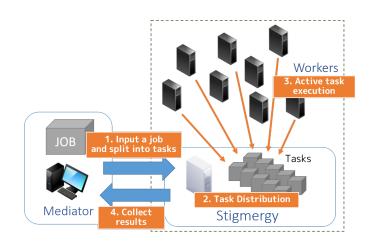

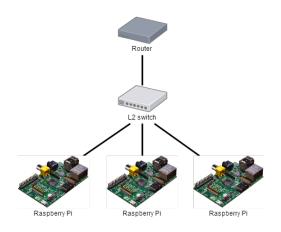

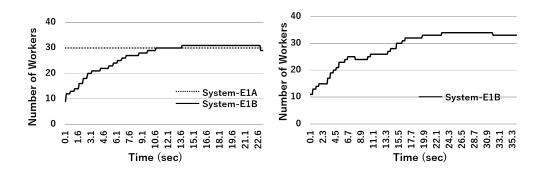

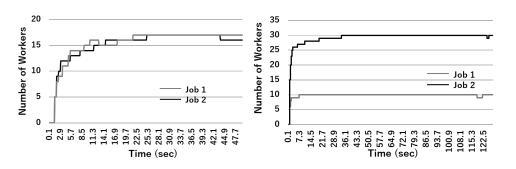

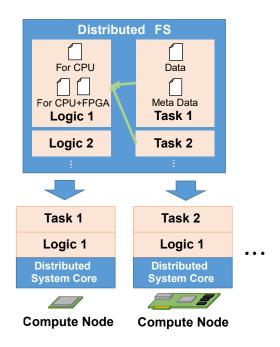

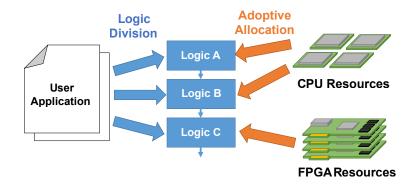

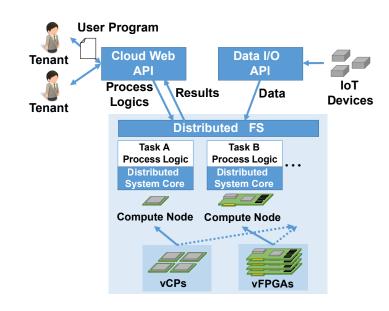

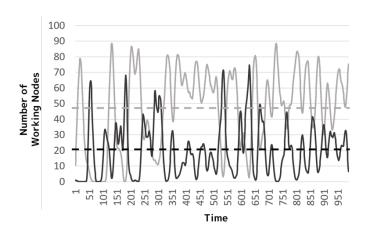

このアプリケーションは,マイクを3つ用いたマイクロホンアレイによって音源の位置を推定し,可視化した位置を HTTP を通して配信するシステムである.